Part Number: INA190

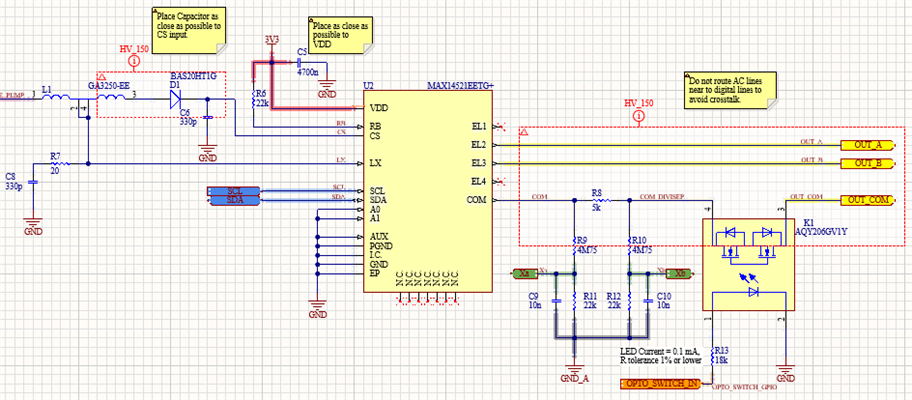

I am an electronics engineer at Laclarée, a French startup, designing electronic eyeglasses for presbyopia correction. In our eyeglasses, we have a MAX14521E for generating a +/- 140V square wave signal needed to the deform the membrane of our lenses. This signal can be considered to be connected to a capacitive load ranging from 0 to 8 nF. We would like to measure the current consumption of this capacitive load connected across OUT_A- OUT_COM or OUT_B- OUT_COM.

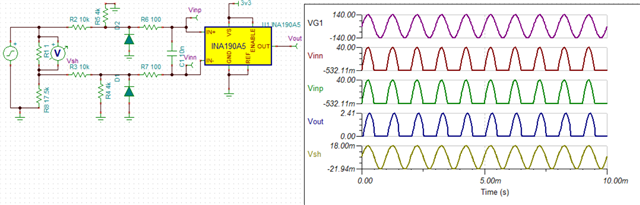

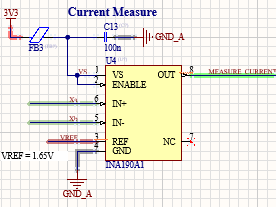

Our measurement and feedback section is placed on the COM line as shown in the figure above. We want to use the INA190 due to its low power consumption. Even though the current measure section is after the load, the voltage on the COM line is still +/- 140V. This complicates the direct measurement of current using the INA190. The output signal of the INA190 is expected to be in the range of 0-3.3V and capable of measuring 0-8mA. I have implemented a voltage divider to reduce the common mode voltage but it is not clear to me if this is the right implementation. Could you kindly help me with this?