Other Parts Discussed in Thread: TIOS101, UCC27517,

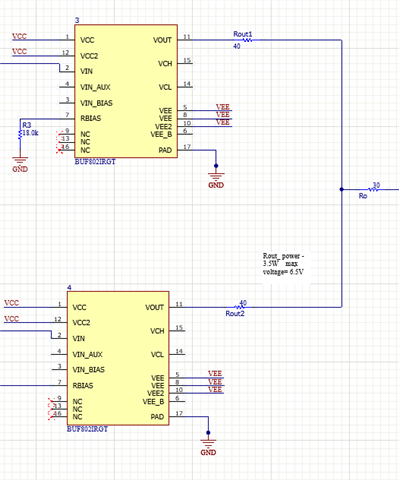

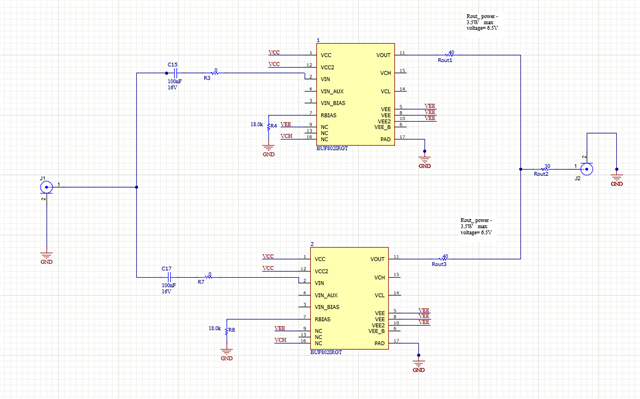

I am using two BUF802s in parallel as my output driver as shown below.

The input to my BUF802s is a square wave.

How to determine how much Propagation Delay is the buffer adding to the two signals? Couldn't find anything specific regarding the delay on the datasheet.