Hi team,

My customer has been using TLV9064 for many years, but the latest batch of TLV9064 seems to have a larger Vos value than before, the codes are 32AG3P0Q0 and 32AG3P0XC.

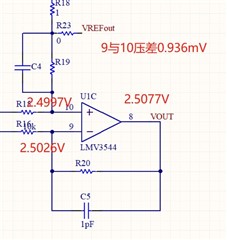

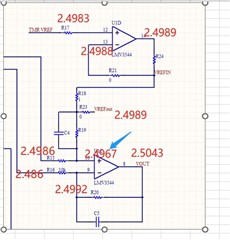

Here are the actual results of the customer's testing. When they do not account for the loss, Vos = 2.4989 - 2.4967 = 0.0022V.

This situation is an occasional issue and the Vos is usually ideal when the customer changes to a new TLV9064 device.

Could you please give some comments for the issue? Thanks in advance!

Regards,

Ivy