Part Number: MF10-N

Other Parts Discussed in Thread: LMF100

Hi,

MF10-N BPF doesn't work according to the design. Help please.

The following schematic is it:

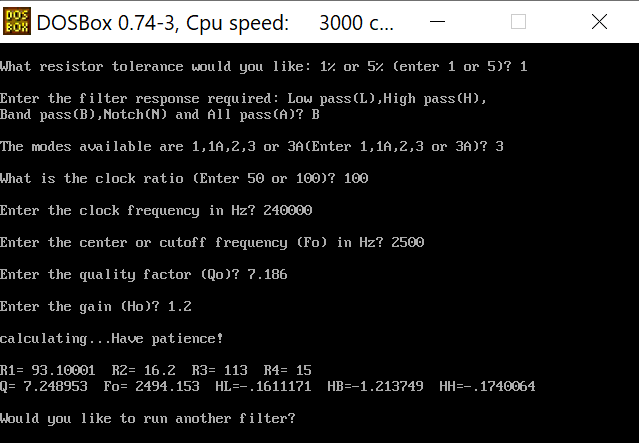

This is an 8th order chebyshev band-pass filter, in which every stage

runs in the mode 3 with the 100:1 clock, and I'm sure I designed it so

as to run with the 0dB gain in the pass-band. The clock supplied is

typically 240kHz, the duty ratio is exactly 50% because of 1/2 divider.

The bode plots shown there are the ones that the LTspice calculated

using the spice model LTC1060, as known as mostly compatible with

MF10-N.

However, the actual gain is too large and the pass-band-width looks

too narrow. The 1st stage, i.e., "IN" through "TP1", behaves especially

funny. The Hobp is calculated as R3*/R1*, so the peak gain should be

near to 180k/150k in the 1st stage, but actually it is too peaky as

shown below:

Does anyone know what I failed?

Thanks in advance.

Regards,