Hello Community,

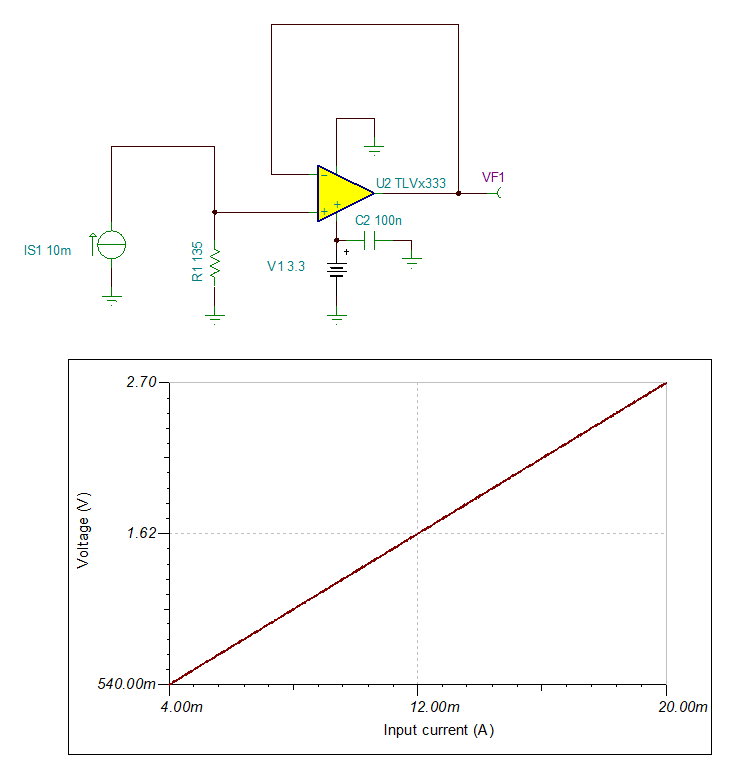

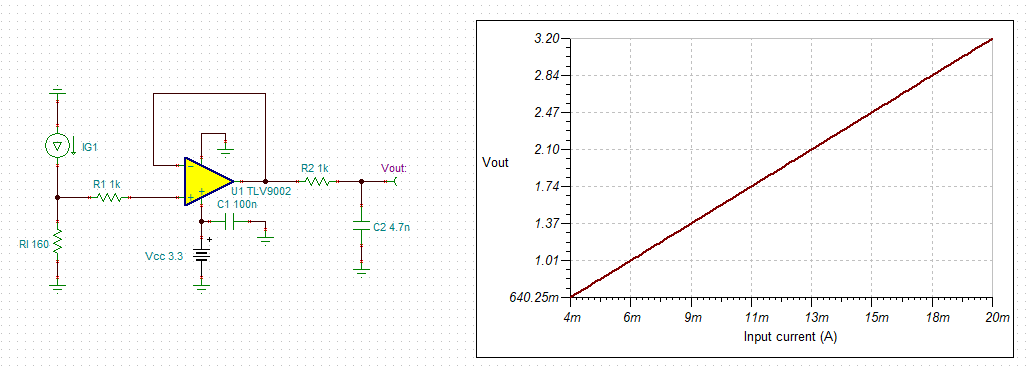

We are working on a highly cost-sensitive Data Acquisition system and seeking your valuable expertise to guide me through the design process. The system involves measuring the voltage drop across a Shunt resistor, which is connected in series to the signal circuit loop. The signal circuit loop can either be a 4-20mA current loop or the secondary side of a Current Transformer (CT).

Measuring Circuit Details:

- Supply Voltage: 0 to 3.3V

- ADC Input Range: 12-bit unipolar, 0-3.3V (adjustable to 2.048V, 2.5V, and 2.9V)

- Expected Bandwidth: Up to 2/3kHz maximum

- Separate grounds for measuring circuit and current loop circuit

Current Loop Circuit Details:

- Supply Voltage: 0 to 36V

- Current signal in the loop 4-20mA

Secondary Side CT Details:

- The CT has a turn ratio of 1:2500

- Shunt Resistor (Burden resistor) can range from 5 Ohm to 50 Ohm (lower the better)

- Ability to adjust shunt resistor value for burden resistor on the secondary side of the CT to match ADC dynamic range based on the current being measured (adjustability is preferred)

I am relatively new to Analog circuits, and my team and I are facing challenges in converting analog signals into the digital domain with the required accuracy & confidence. We are looking for your guidance to navigate this design process efficiently.

The system will be utilized to measure fairly slow-moving physical quantities like Temperature, Pressure, etc., via the 4-20mA current loop. Additionally, we will also be measuring current with a lower shunt resistor across a Current transformer.

- Acceptable Error: 0.2-0.4% max

- Using low-cost MCU with 5 built-in 12-bit ADCs (hardware oversampling) for improved SNR.

- Measuring slow-moving physical quantities like Temperature, pressure etc via a 4-20mA loop.

- Measuring current consumption with a smaller shunt resistor across the Current transformer's secondary side.

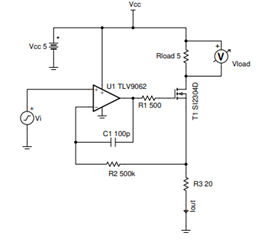

- OpAmp Shortlisted: TLV9062, TLV9002, TLV07,

- Current Sense Amp Shortlisted: INA351, INA181, INA199.

- Seeking circuit design suggestions: minimal discrete components, cost-optimized & highly integrated solutions.

Thank you in advance for your support and valuable input.