Other Parts Discussed in Thread: TINA-TI

Hello,

I'm working on a design revision for a circuit that uses the OPA552. I have a few questions I'd like to resolve to understand why our current design might be flawed. We are seeing a lot of high frequency noise at the output signal of the op amps.

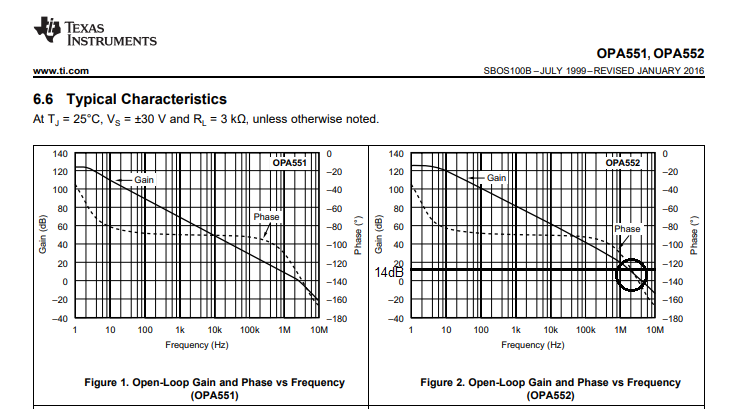

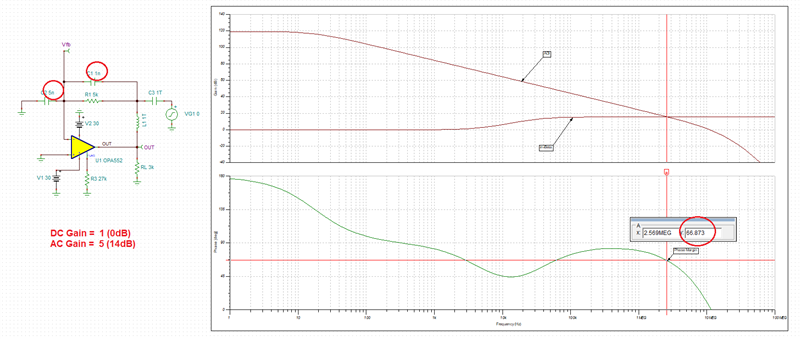

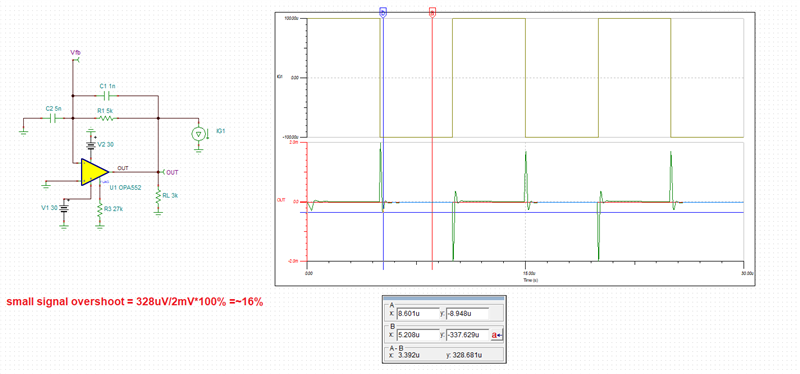

1. After reading the datasheet on page 1, I see that this op amp is optimized for gains of 5 or greater. In our application, we have circuits where the OPA552 has gains of 1 and 2. In these designs, we are seeing a lot of high frequency noise at the output of the op amp. Does "optimized" mean that the op amp is unstable for gains below 5? Would you expect to see this high frequency noise as a result of using the low gains?

2. I see that the op amp has three V- pins in the SOIC-8 version (pins 1, 4, and 5). On page 17 of the datasheet, there is a note that pins 1 and 5 should not be attached to the negative power supply and should not be used as current carriers for the SOIC-8. Does this note only apply when V- is connected to a negative power supply or also when V- is grounded? We have the op amp in our application running with 24 V at V+ and V- is grounded. I'm thinking this could also be a cause of our issues. The datasheet mentions to expect performance reductions when doing this. What kind of performance reductions can be expected? Would this cause high frequency noise? I also disconnected pins 1 and 5 from ground and retested to find the high frequency noise still there. Could doing that have caused permanent damage to the chip, or is this a sign that this is not the root cause of the issue?

Any help would be much appreciated.

Sincerely,

Mike