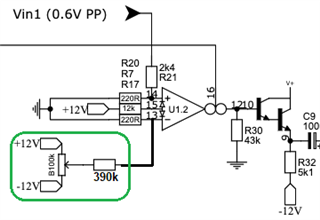

Hello! I need help to fix an issue I'm facing in a design involving 2 halves of a LM13700 as a simple amplifier.

As you can see in the schematic, Iabc of each half of the LM13700 is maximum 500uA.

Vin1 and Vin2 are normally 0.6V PP but for this example, they are both 0V in order to show the issue. So no signal goes through the non-inverting inputs!

Iabc are controlled by a potentiometer and an external voltage control.

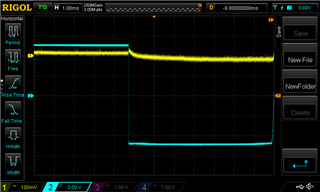

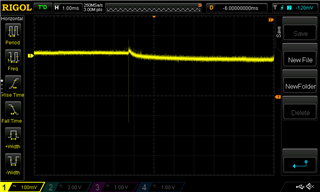

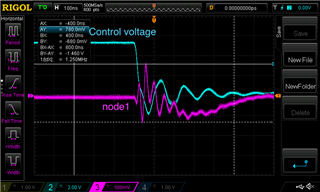

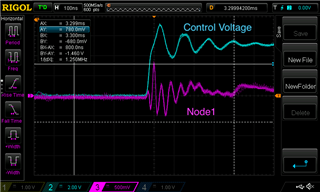

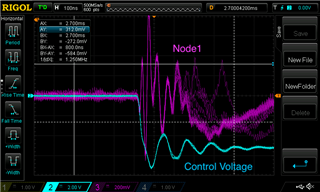

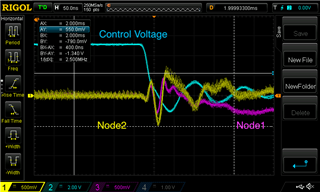

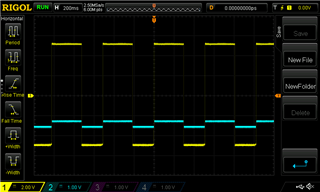

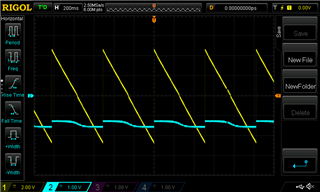

I noticed something very unpleasant when I feed a control voltage (on the left of the schematic). this is 10VPP and it also appears at the output as Captured by the oscilloscope. This is unexpected to me since if no signal is applied to the non-inverting inputs, I expect nothing at the output as well.

Do you know why this is happening and how i can avoid it?

Thanks

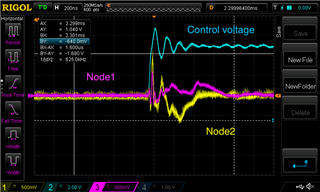

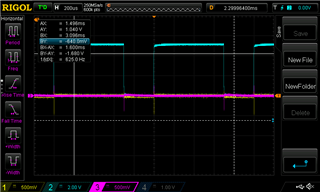

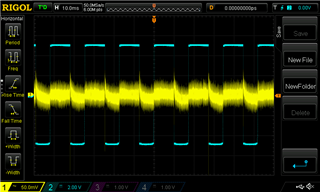

this made it much much better and now the signal at the output is around 50mV that is more than acceptable. Thanks for the advice.

this made it much much better and now the signal at the output is around 50mV that is more than acceptable. Thanks for the advice.