Other Parts Discussed in Thread: OPA192, OPA2156, OPA828, OPA827, OPA992, OPA323, OPA4323, OPA322, INA851,

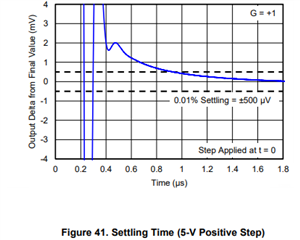

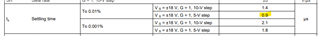

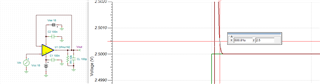

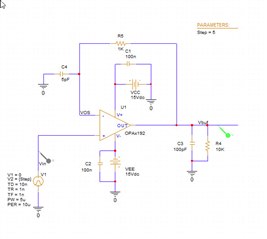

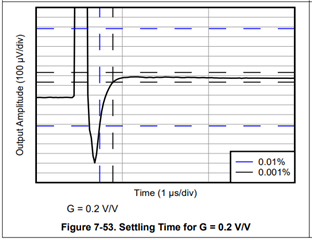

I'd like to know the circuit topology when the settling time is specified. The Pspice model I use from the website gives me a much better settling time than the typical that is shown in the datasheet.

- Datasheet page 9 ts. I see Rload is 10K (from the top of the page), any load capacitance?

- Note that the typical step responses use a Rload of 1K and Cload of 10pF. There responses are even faster than the typical that is specified in the data specification table.

Thanks,

-John Gray