Dear Experts,

I need your experties to design a DAC output smoothing amplifier.

I am using DAC Evaluation board DC2459A with LT1668, at 10MHz to 20MHz CLK and the Signal will be of 1MHz to 7MHz. I get stair case waveform at the output of DAC. So need a smoothing circuit at output stage. Further I will be driving piezo.

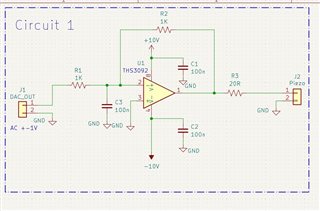

I have tried few circuits designs. In Circuit 1 I get 1MHz smooth waveform but than it starts attenuating as I go higher. I figured out that by decreasing C3 (100n) starting point of attenuation shifted to 2MHz,3MHz, and so on but the waveform is not smooth as with 100n.

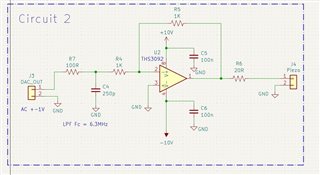

In Circuit 2 I have added LPF at before Rin(R1) whose cutoff frequency is 12MHz but here at just 1MHz staircase is been observed at the output of the op amplifier.