Part Number: OPA2156

Other Parts Discussed in Thread: TINA-TI

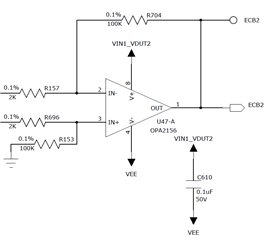

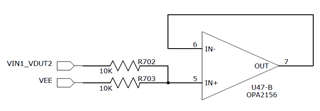

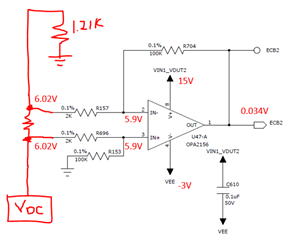

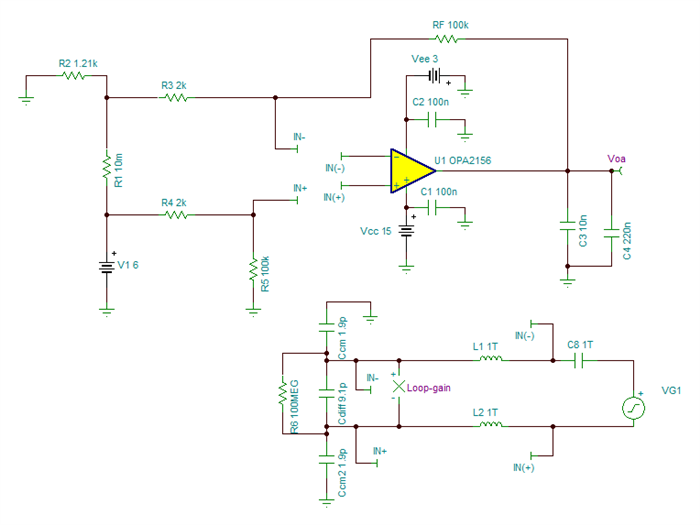

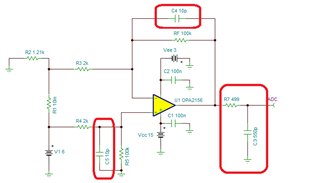

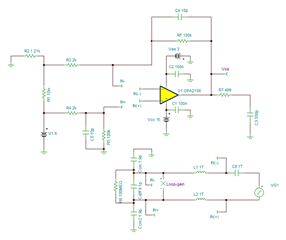

I'm using the OPA2156 for a very simple circuit measuring drop across a .01 Ohm shunt resistor. My circuit operation seems to perform as expected but I was surprised by the temperatures I was reading on the IC when using a thermal camera. The positive rail is biased with a 15V supply and the Negative (VEE) is -3V. There is a dual op-amp package although I'm only using one of the channels. My test conditions are running board at 25C ambient, the shunt resistor is not loaded so there is 0V drop. When there is no voltage applied to the shunt resistor my IC is sitting around 40C which seemed reasonable to me given the Pd and thetaJA of 119degC/W. If I apply 1V to the shunt resistor the IC temps jump to 70C, if then increase the shunt resistor voltage source to 6V the IC then jumps to 90C. The output of the op-amp is driving the input of an A2D converter although in my examples above the voltage on the output stays below 50mV as there is no load on the shunt.

I don't see how changing the shunt resistor voltage while not driving a load on the output is causing such high increases on my IC temps. I was thinking it would take almost 400mW of additional power to raise from 40-90C. Is there something I'm missing with how my voltage inputs are impacting power dissipation?