Other Parts Discussed in Thread: TINA-TI

Hi Amps Team,

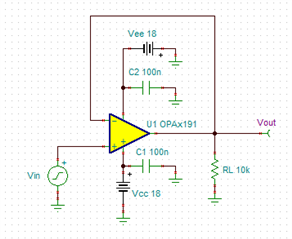

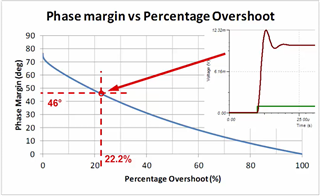

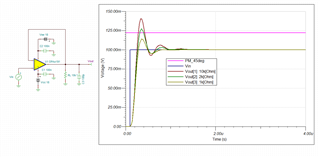

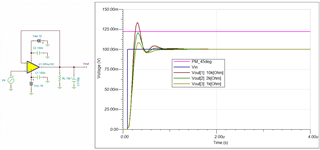

We are working to optimize the PCB by reducing the number of components in the schematic. One possible way to reduce components would be to remove the snubber circuit. Please note that the datasheet for the OPA2191 component recommends placing an RC circuit with unity-gain configurations that have no/light DC loads. Would you please advise what would be the maximum load that we could have without said snubber circuit? Thank you for your help.

Best regards,

Nic Gough