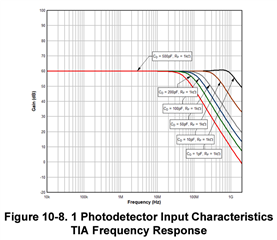

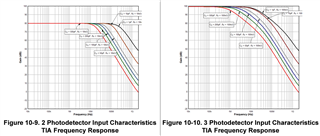

Referencing Figure 10-8, 10-9, and 1-10 (pages 26-27 of OPA855 datasheet). Increasing C_D results in a lower bandwidth.

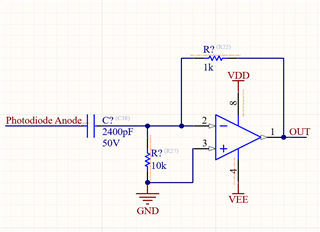

My application includes a reverse biased photodiode, with an RC HPF (series 2400pF, shunt 10kOhm) between the photodiode anode and the OPA855 input (see rough schematic below).

My questions:

- Will including the 2400pF capacitor reduce the bandwidth, as described in Figures 10-8 through 10-10?

- If so, how should one maximize bandwidth while blocking DC?

- Is it not important to block DC in a photodiode application such as this?