Other Parts Discussed in Thread: OPA657

Dear Engineers,

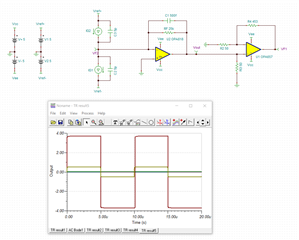

I want to make a circuit design for LiDAR receiver application.

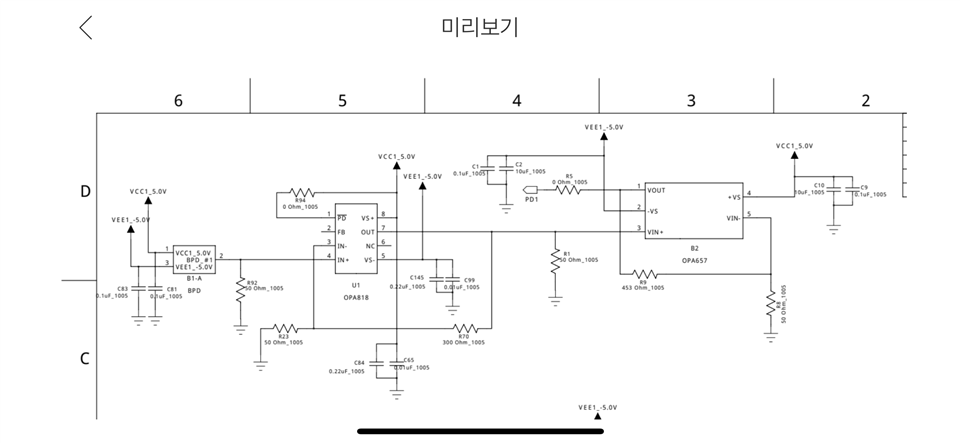

I made a first circuit as a first photo below, but it doesn’t work properly. So I hope to listen to your comments.

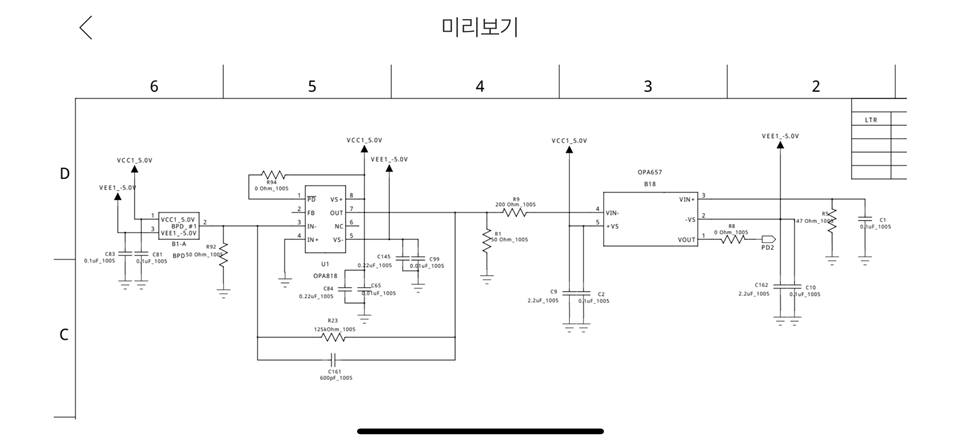

please review my two circuits shown below

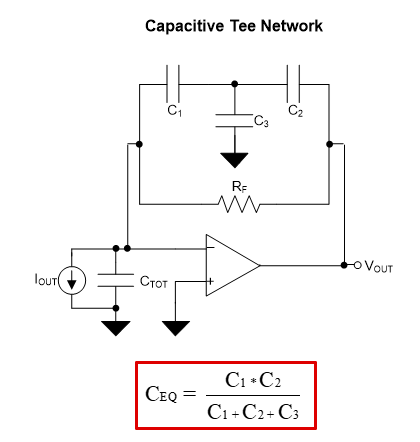

The second design is what I got from the forum as below.

and I hope somebody let me know the reason why second circuit has a inverter function.

my previous post