Other Parts Discussed in Thread: INA333

Hello,

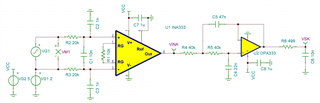

I have a design that uses the INA333 as the instrumentation amplifier and main gain stage for a relatively slow (<10Hz) but highly precise input signal. The input signal has a negative leg of constant two volts with the differential signal riding on top of that at ~10mV to ~320mV.

So at full scale range the input is roughly...

- Vcm = 2V+320mV/2 = 2.16V

- Vdiff = (320mV - 10mV) / 2 = 155mV

I want to interface this signal to a 5V referenced ADC and so I am using the INA333 with a nominal gain of (1+100/10) = 11.

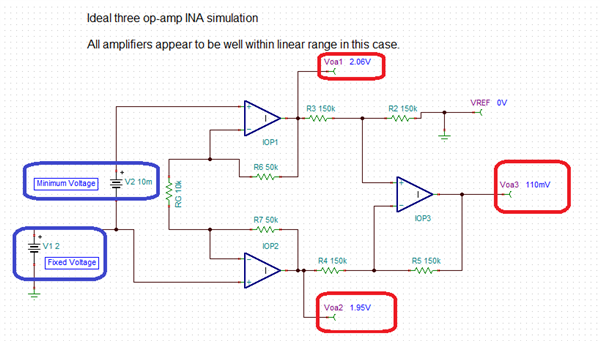

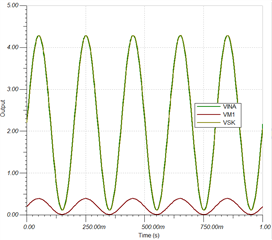

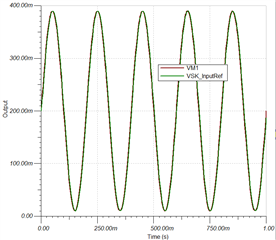

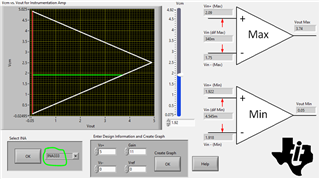

I have this simulated in TINA TI and things appear to work great...

(NOTE: TINA simulation was with Vdiff,max = 390mV, a more conservative demonstration)

Input Vs Output Waveforms:

Input Vs Output/Gain Waveforms:

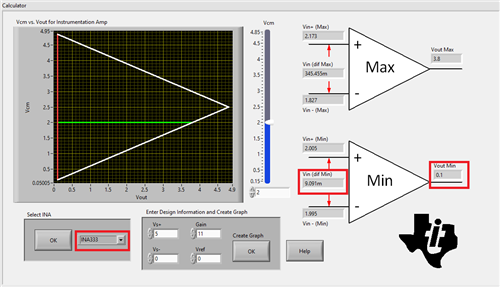

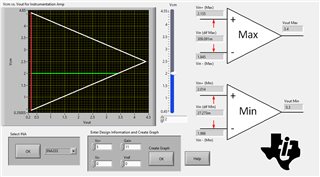

But just to double check that the sim isn't misleading me I've been using the TI Analog Engineer's Calculator Tool and the parameters look good...

Plenty of margin for the 320mV even with quite a bit of slack on the 2V Vmin setpoint (as low as 1.75V is sufficient, going higher should just help). And for the 10mV minimum differential there also doesn't seem to be any issue.

....

But here's the kicker.

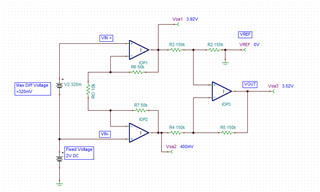

My coworker has a newer version of the TI "Analog Engineer's Calculator" installed and it shows that this design will not close and actually has negative margin... But I can't figure out why.

Output from his (newer) version of the tool:

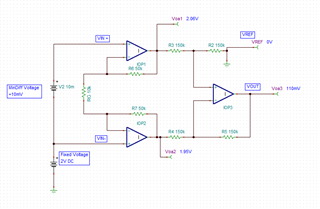

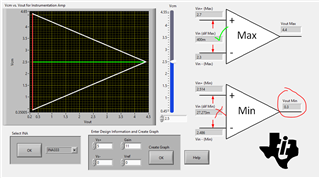

If I adjust the negative leg setpoint to be larger (say 2.5V instead of 2V) then I am able to get the maximum differential to close... but the minimum voltage is limited to 27mV no matter what common mode I use... Seemingly mapping to a hard limit Vout Min of 0.3V.

VCM = 2.5V:

We swept the entire possible Vcm range with these Vs+/Vs-, Gain, and Ref settings and it shows a static 27mV minimum differential and a constant Vout Min of 0.3V...

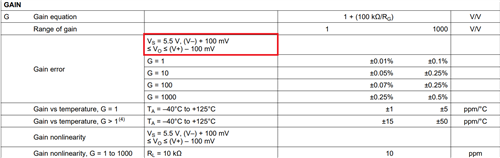

So yeah, we are confused -- the datasheet for the INA333 implies that the device can swing within 50mV of the output, so I don't understand what is driving this minimum voltage of 0.3V... I also don't understand why the old version of the Analog Engineer's Calculator supported our design as having good margin (as does TINA TI simulation) while the new version shows that it is a dud.

Can someone from TI advice? Should we trust the newer version of the calculator and redesign accordingly?

This is fairly time critical (we were just about to order dev boards before we caught this and the boards and lead times are quite expensive/long)/