Other Parts Discussed in Thread: OPA192

Hi Team,

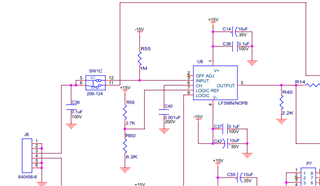

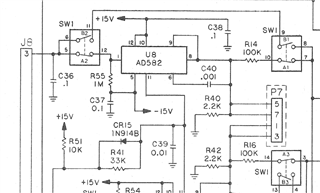

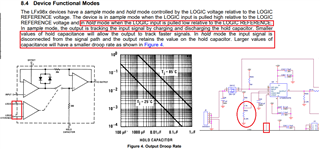

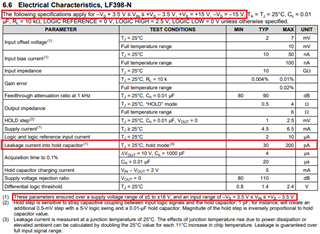

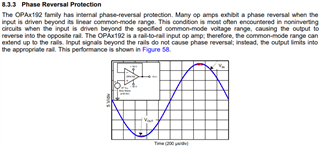

In our existing Design AD582KD (Sample and Hold amplifier) is used. With TI suggestion, In new design we are using LF398-n. During Bench level testing we noted that, In hold mode Voltage decreases till -13.8V from 0 V. But in AD582KD IC Voltage increases to +13V. I have attached both circuit design. Is it acceptable? Why it is increasing, If IC in sample mode means it should be in constant voltage right? Please provide the reason.

Regards,

Pradeepraj M