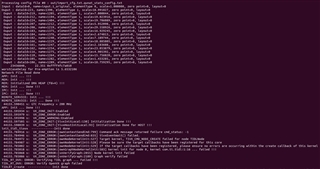

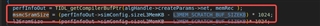

./TI_DEVICE_armv8_test_dl_algo_host_rt.out s:out/import_cfg.txt.qunat_stats_config.txt

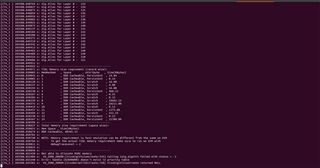

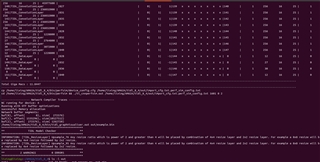

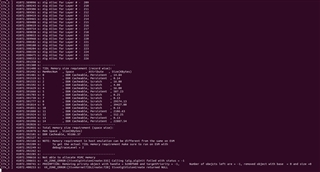

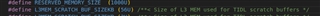

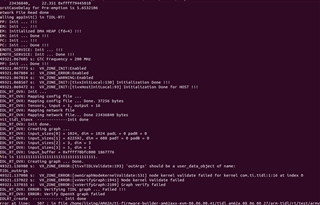

C7x_1 ] 1159526.343922 s: TIDL Memory size requiement (record wise):

[C7x_1 ] 1159526.343957 s: MemRecNum , Space , Attribute , Size(KBytes)

[C7x_1 ] 1159526.343997 s: 0 , DDR Cacheable, Persistent , 14.84

[C7x_1 ] 1159526.344036 s: 1 , DDR Cacheable, Persistent , 0.14

[C7x_1 ] 1159526.344072 s: 2 , DDR Cacheable, Scratch , 16.00

[C7x_1 ] 1159526.344109 s: 3 , DDR Cacheable, Scratch , 4.00

[C7x_1 ] 1159526.344144 s: 4 , DDR Cacheable, Scratch , 56.00

[C7x_1 ] 1159526.344181 s: 5 , DDR Cacheable, Persistent , 468.21

[C7x_1 ] 1159526.344218 s: 6 , DDR Cacheable, Scratch , 0.25

[C7x_1 ] 1159526.344255 s: 7 , DDR Cacheable, Scratch , 0.13

[C7x_1 ] 1159526.344291 s: 8 , DDR Cacheable, Scratch , 19662.13

[C7x_1 ] 1159526.344326 s: 9 , DDR Cacheable, Scratch , 26211.00

[C7x_1 ] 1159526.344362 s: 10 , DDR Cacheable, Scratch , 0.13

[C7x_1 ] 1159526.344397 s: 11 , DDR Cacheable, Persistent , 1375.88

[C7x_1 ] 1159526.344439 s: 12 , DDR Cacheable, Scratch , 512.25

[C7x_1 ] 1159526.344476 s: 13 , DDR Cacheable, Persistent , 0.13

[C7x_1 ] 1159526.344513 s: 14 , DDR Cacheable, Persistent , 11780.09

[C7x_1 ] 1159526.344543 s: --------------------------------------------

[C7x_1 ] 1159526.344572 s: Total memory size requirement (space wise):

[C7x_1 ] 1159526.344596 s: Mem Space , Size(KBytes)

[C7x_1 ] 1159526.344620 s: DDR Cacheable, 60101.15

[C7x_1 ] 1159526.344646 s: --------------------------------------------

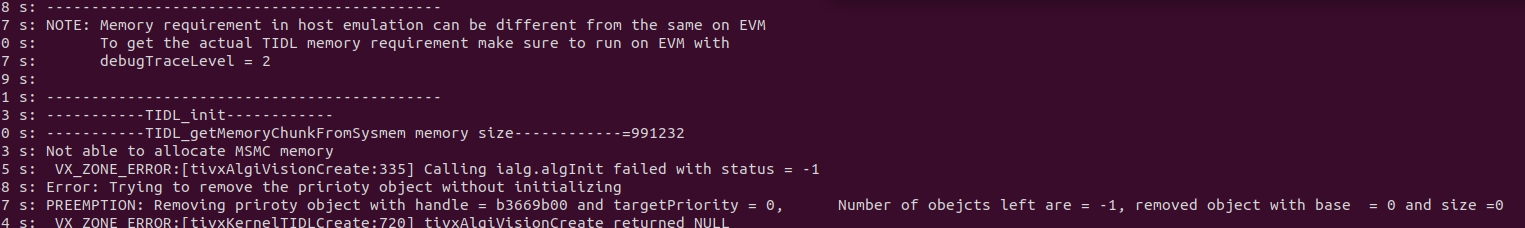

[C7x_1 ] 1159526.344686 s: NOTE: Memory requirement in host emulation can be different from the same on EVM

[C7x_1 ] 1159526.344728 s: To get the actual TIDL memory requirement make sure to run on EVM with

[C7x_1 ] 1159526.344755 s: debugTraceLevel = 2

[C7x_1 ] 1159526.344767 s:

[C7x_1 ] 1159526.344790 s: --------------------------------------------

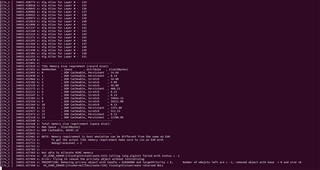

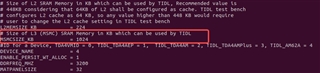

[C7x_1 ] 1159526.349390 s: Not able to allocate MSMC memory

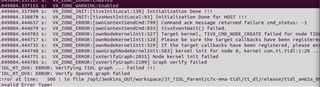

[C7x_1 ] 1159526.349439 s: VX_ZONE_ERROR:[tivxAlgiVisionCreate:335] Calling ialg.algInit failed with status = -1

[C7x_1 ] 1159526.349492 s: Error: Trying to remove the pririoty object without initializing

[C7x_1 ] 1159526.349568 s: PREEMPTION: Removing priroty object with handle = b2b90d00 and targetPriority = 0, Number of obejcts left are = -1, removed object with base = 0 and size =0

[C7x_1 ] 1159526.349613 s: VX_ZONE_ERROR:[tivxKernelTIDLCreate:737] tivxAlgiVisionCreate returned NULL

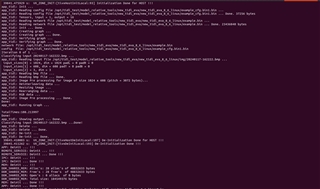

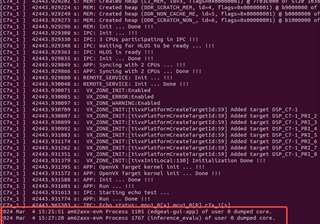

2024 Feb 20 21:24:44 am62axx-evm adjtime failed: Invalid argument

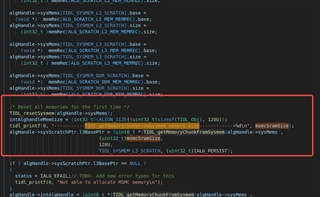

why i can not able to allocate MSMC memory in am62axx-evm

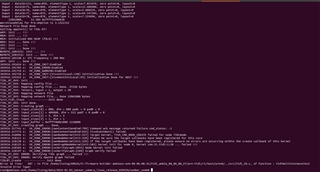

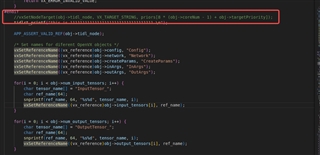

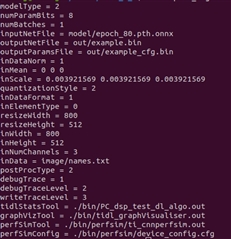

this is import_cfg.txt.qunat_stats_config.txt

inFileFormat = 2

numFrames = 1

postProcType = 0

postProcDataId = 0

quantRangeUpdateFactor = -1.000000

inData = /home/lixing/data/2024-01-03_sensor_camera_linux_release_HIRAIN/number_node/image/names.txt

outData = "/home/lixing/data/2024-01-03_sensor_camera_linux_release_HIRAIN/number_node/out/import_cfg.txt_stats_tool_out.bin"

netBinFile = /home/lixing/data/2024-01-03_sensor_camera_linux_release_HIRAIN/number_node/out/example.bin

ioConfigFile = /home/lixing/data/2024-01-03_sensor_camera_linux_release_HIRAIN/number_node/out/example_cfg.bin1.bin

flowCtrl = 35

writeTraceLevel = 3

debugTraceLevel = 2

traceDumpBaseName = /home/lixing/data/2024-01-03_sensor_camera_linux_release_HIRAIN/number_node/out/import_cfg.txt