Other Parts Discussed in Thread: TLV1851, ATL431, TL331B

Hello,

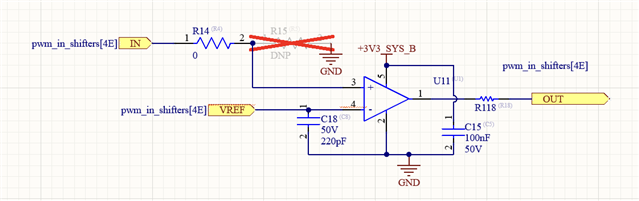

I have TLV1851 with 3v3 supply, IN- @ 2.5V using for PWM logic level translation from 5Vmax, 7Vmax, 10Vmax pwm signals.

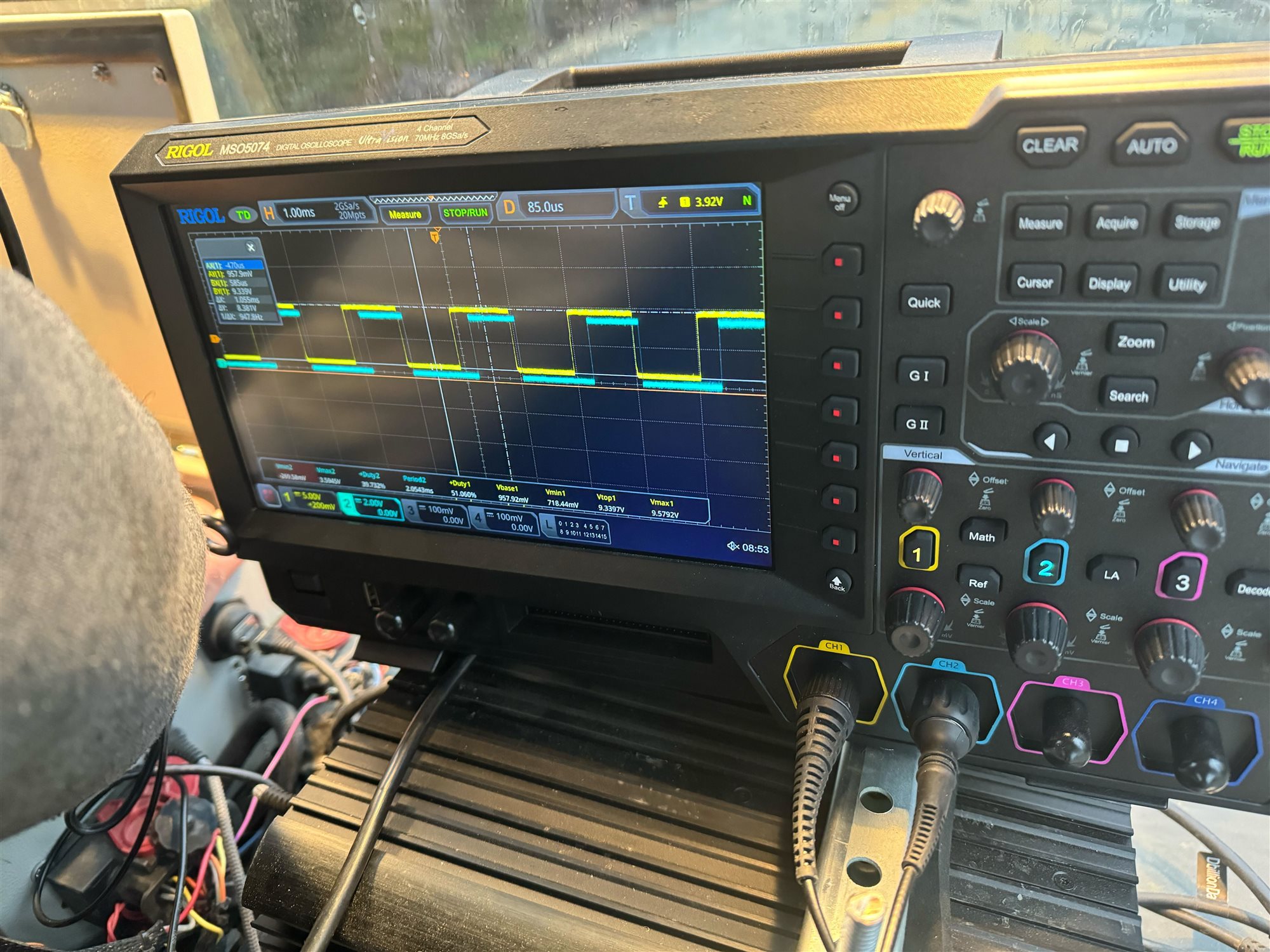

Output is high impedance, and actually the slew rate is very high so its evident there is no loading. you can't see it in the below scope shots but trust me i zoomed way in and its sharp af.

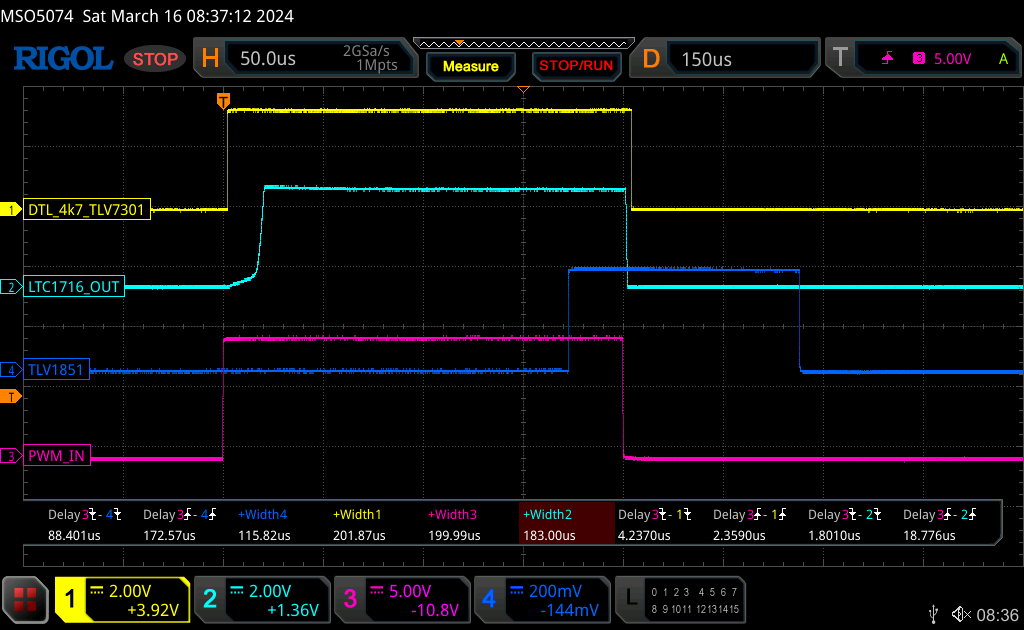

All input signals are 50% duty 500hz so period is 2ms basically.

Below is schematic vref 2v5 is coming from atl431 voltage reference. 3v3 is rock solid.

First image shows 5Vin pwm second 10V pwm. The yellow/ch1 is PWM input, blue is output, measured directly at pins of tlv1851. There is consistently 300us-400us rising prop delay and 60-100us falling prop delay across all channels.

Yes, the probe and scope are working correctly, no delay on ch2. we can probe the same signal and they are both correct.

We also read the signal from GPIO which is why we noticed this issue because the duty cycle read was completely off compared to simple NMOS based level shifter or another CMOS buffer.

The delay is an order of magnitude higher than I expect from datasheet e table, on the order of 10us. Additionally, the prop delay matching is so huge we get truncation of the pwm signal. You can see the rising tpdlh is approaching half of the high pulse, which itslef is 1ms on time, so its like unbelievable large.

I'm trying to understand how i am using this part wrong. Because the inputs are overdriven susbstantially so i would expect a mucsh lower tpdlh.

Why is the prop delay so high and not captured in d/s specs?

Why is the pulse width distortion this insane?

I mean the beyond VCC inputs are not really useful if this thing compares things this slow, we can basically only trust it with a 1hz signal.

Best

Dimitri