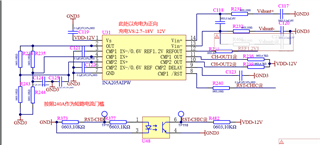

During initialization, when the INA205 cmp1 reset pin is pulled high and cmp1 in has no input, cmp1 out outputs a high level

Can you see what the reason is, please

-

Ask a related question

What is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.