- Ask a related questionWhat is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Dear all,

I want to use a reference design form Texas instrument as a reference for my layout for OPA838, I noticed this reference design is a 4-layer board:

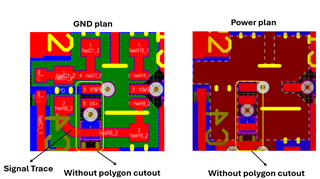

As we can see in the picture, there are polygon cutout both for GND and power plan, but I noticed, there is no polygon cutout for pin 5,6,2, which are positive and negative and enable pin, why we have kept GND and power plan underneath these pins?

My second questions is:

In this layout I can see under the signal trace (Signal Trace in the picture), we have discontinuously of the GND underneath the trace, can this cause any issue from layout standpoint? considering a s a genal rule for high speed routing we should provide a return path for signal trace, this return path is GND plan underneath the signal, but in this case we do not have it or we have it but in a discontinuous way. Please let me know if I'm right or not, if yes, how we can optimize the layout?

Regards,

Hi Behnam,

The reason for removing the power/ground planes is to limit parasitic capacitance. Having copper planes split with a dielectric will cause this. The reason we care about this with high-speed parts is because at the higher frequencies, the few pF that these planes create at a given node will start to affect the circuits performance. Given this information, the reason we only remove the planes at the inverting node and the output pin is because parasitic capacitance from the planes will seriously affect the performance of the circuit. Having parasitic capacitance at the PD pin or supply pins will do very little to the functionality of the circuit. Having some parasitic capacitance at the output pin or inverting node will lead to stability issues. As for your second question, yes that is true that the lack of ground under the feedback path with lead to some higher inductance, however the stability issues by having the planes under this trace will affect the performance of the circuit much more. Inductance is a huge concern for longer traces, so having a GND under these traces is crucial, but when considering the short path of the feedback network which should be laid out as tight as possible, the concern with stability is much greater. As for a better layout we recommend looking at our EVM layouts as they highlight best practices.

Best Regards,

Ignacio

Hello @Ignacio Vazquez Lam1

Thank you very much for the nice explanation, it was very very useful.

First of all I need to mention that these pictures are screenshots from a TI reference Altium design that I previous got form TI as a reference layout for OPA838DBVEVM (file name: HSP024A_ASCII.PcbDoc. Then I wonder why they did not use a continuous ground plane for underneath the signal? should I do change it to a continuous GND under the signal? or is this possible that this reference design is not the most recent one? maybe can you please share with me an optimized layout for OPA series in general? I'm a bit unsure what should I use as a refence design at this point. Please see the attached file (the reference design that I got form TI: HSP024A_ASCII.PcbDoc):

Hi Behnam,

They didn't use a continuous ground plane for the reason mentioned above to reduce parasitic. We would recommend removing the ground and power planes under the feedback trace. There are other examples where we remove these layers under this portion of the circuit, so it is a fairly common practice with our EVM designs.

Best Regards,

Ignacio