Tool/software:

Hi all.

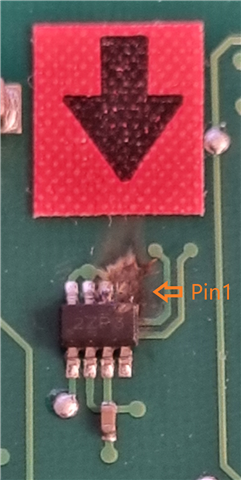

I'm using INA241A3-Q1 shunt amplifier. I have some problem. We got boards from assembly. During testing one of INA241A3-Q1 has burnt:

I'm trying to understand what could be a cause of it.

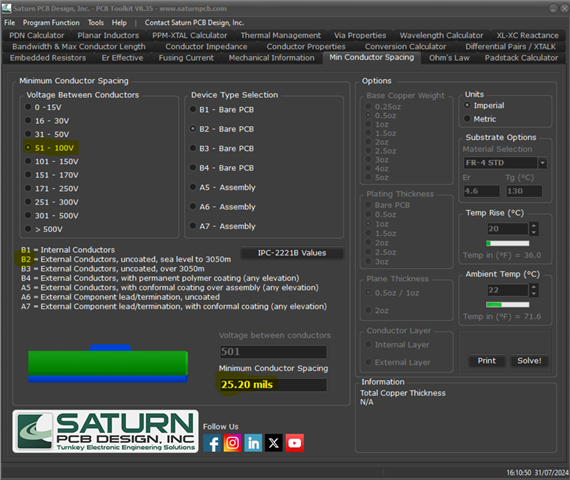

I've checked that there should be a minimum gap of about 25mils at an external layer (I'be used Saturn PCB):

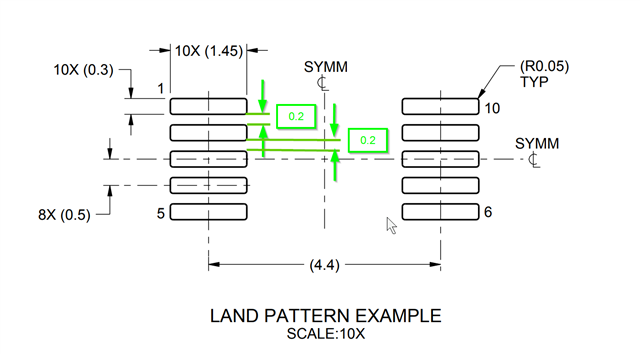

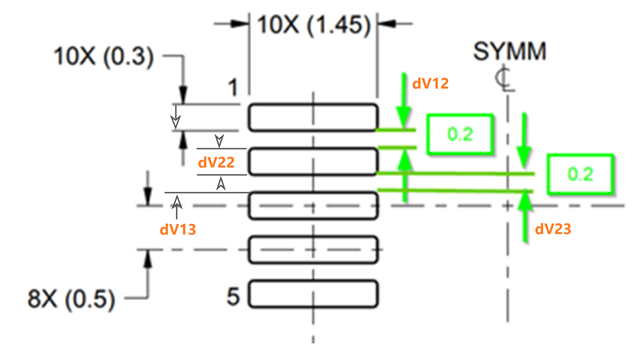

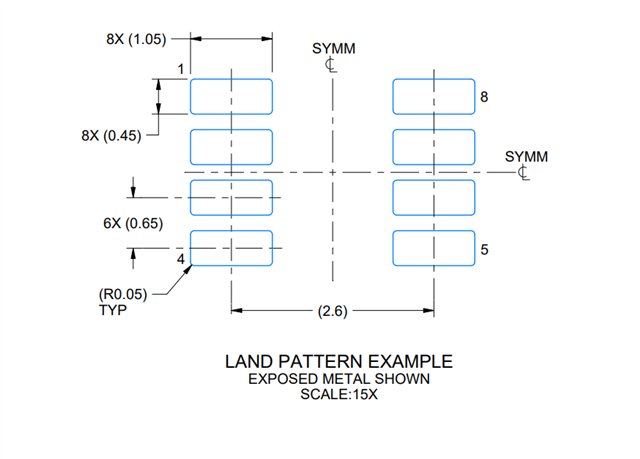

However, the recommended gap between adjacent pins according to datasheet is 0.2mm (8 mils):

This component is capable to withstand common mode voltages of up to 120V!

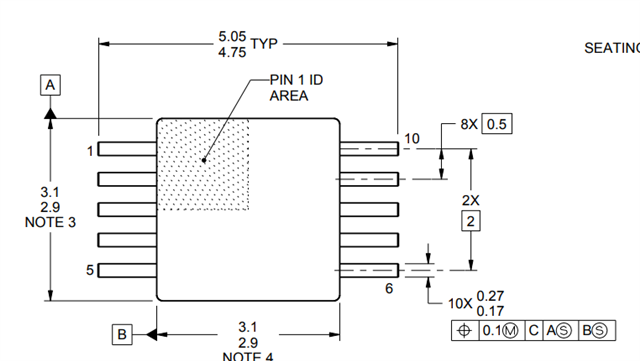

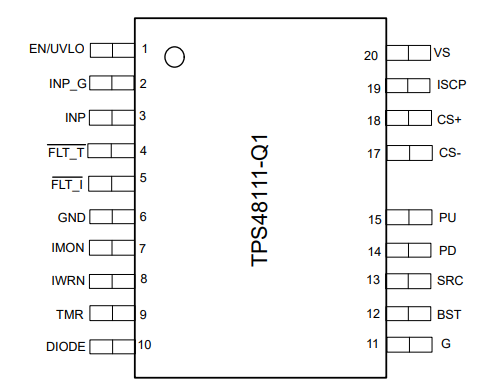

Since pin 1 is a "+" terminal, and pin 2 is GND, and according to clearance/creepage calculation it seems to be a problem.

I'm trying to investigate this problem, and woild like if someone has an idea.

Sincerely,

Alex