Tool/software:

Dear Technical Supporters,

Hope you are doing well.

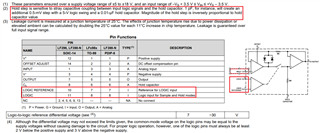

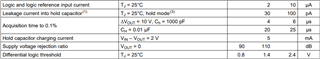

I'd like to get some information about Null offset of LFx98 on Output Line during power up.

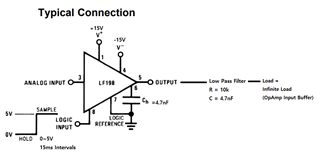

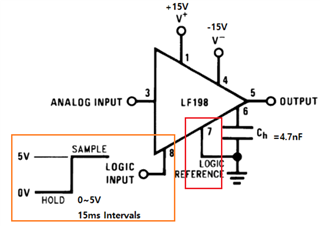

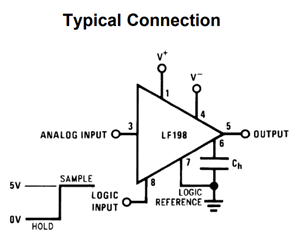

In my schematic, it was designed with ±15V power supply and same as below.

I'd like to get 0V voltage on output when power up, but there were about 400mV on the output although there was 0V on Analog Input.

(There are 4 channels in my design and they have outputs as about 400mV as.)

I already checked Logic Input but there was nothing signal logic high during power up.

Q1. If there are a few difference with ±15V Supply voltage, would it affect output offset voltage?

Q2. If not, are there something factors that make offset on output line?