Part Number: LMH7322

Tool/software:

Hi, and thanks for reading this!

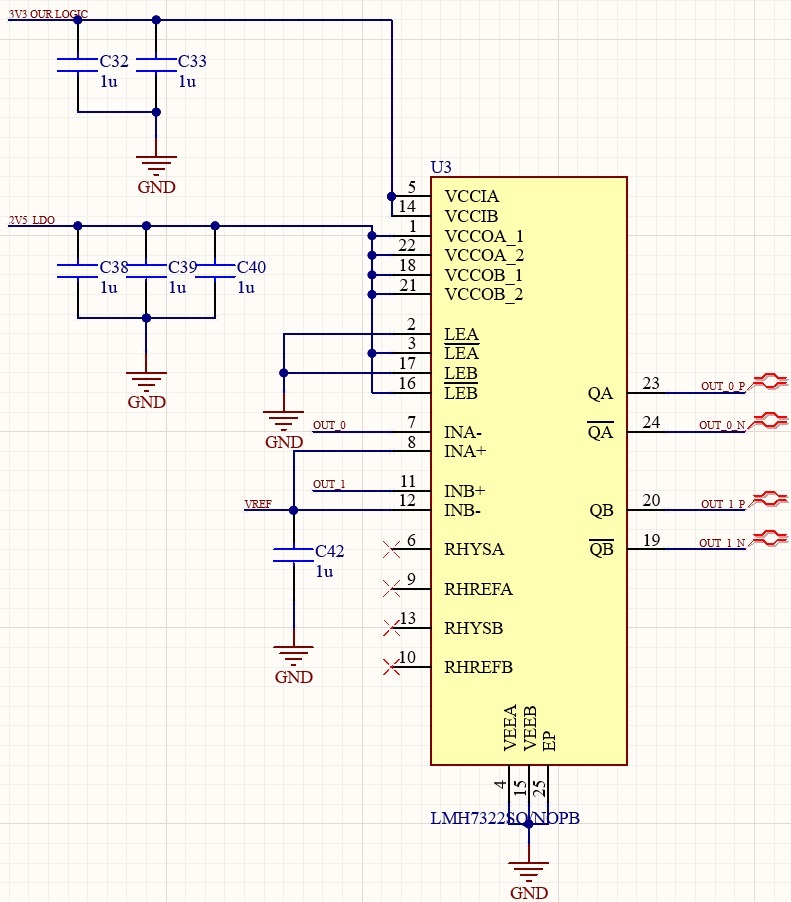

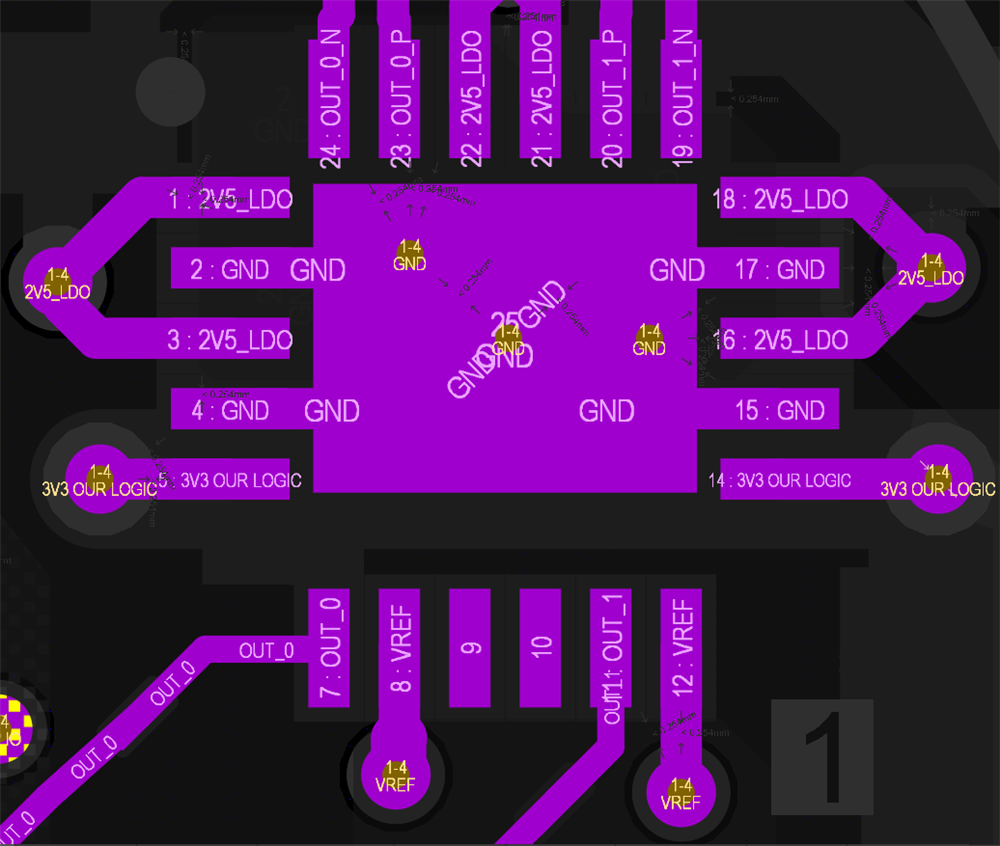

I have a PCB where a custom chip produces four LVCMOS 1.2V outputs - named OUT_0, OUT_1, OUT_2, OUT_3 - which I had to convert to LVDS. I considered implementing two LMH7322SQ/NOPB comparators with 0.6V reference voltage to do this. However, the outputs are stuck just above 1V. My implementation is the following (identical for the two comparators):

All voltages are set correctly.

I know pins 6 and 13 are missing. That was my doing, as I did not want any hysteresis I left them unconnected (and tried to get a signal going under the chip, but didn't do it in the end). I suppose the problem is not connecting any resistance to pins 2 and 3 (I did not want any latching function)., but I'm not sure.

Thank you for your time!

MR