- Ask a related questionWhat is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Tool/software:

It is not a differential output.

Signals in-phase are output.

What is the cause?

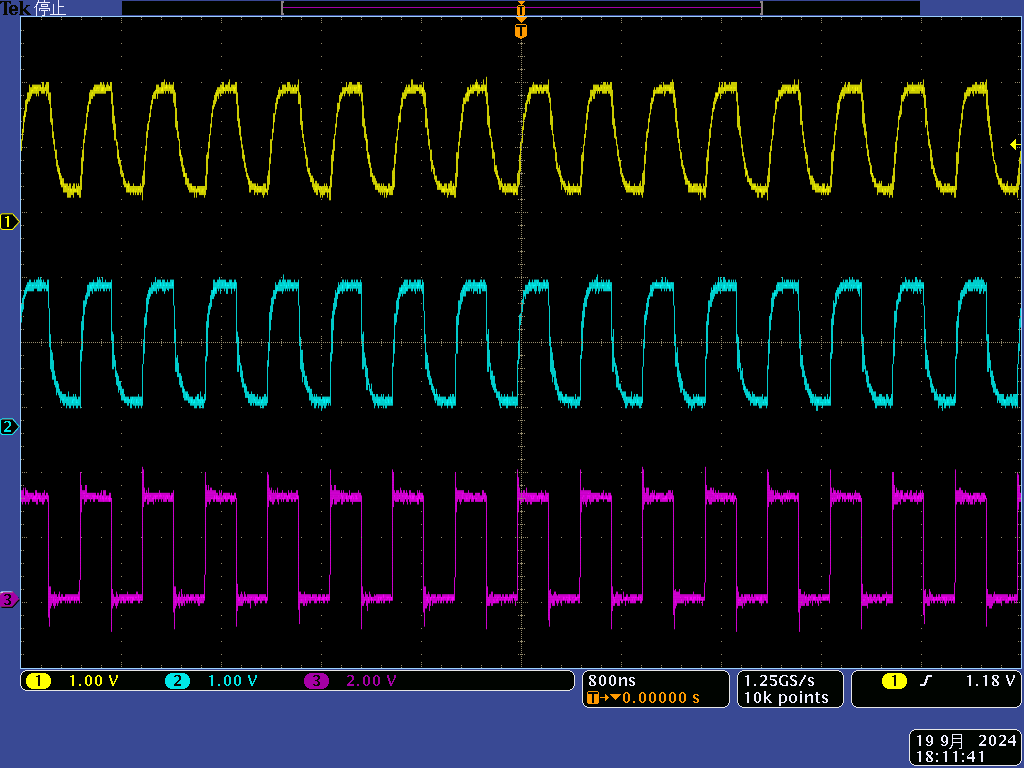

CH1:DIFF_OUT_N

CH2:DIFF_OUT_P

CH3:DIFF_IN

Hi,

Thank you for sharing the schematic and signals. This is definitely something that should not be happening. Could you share more information about the input signal such as the Vpp and offset? I was also wondering if you probe the outputs directly (prior to the coupling capacitors), do you see the same result?

Best Regards,

Ignacio

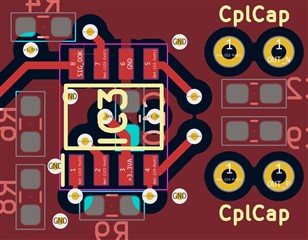

We apologize. The output signal was measured before coupling capacitors.

VREF is input generated by resistively dividing VS+. A bypass capacitor is also attached.

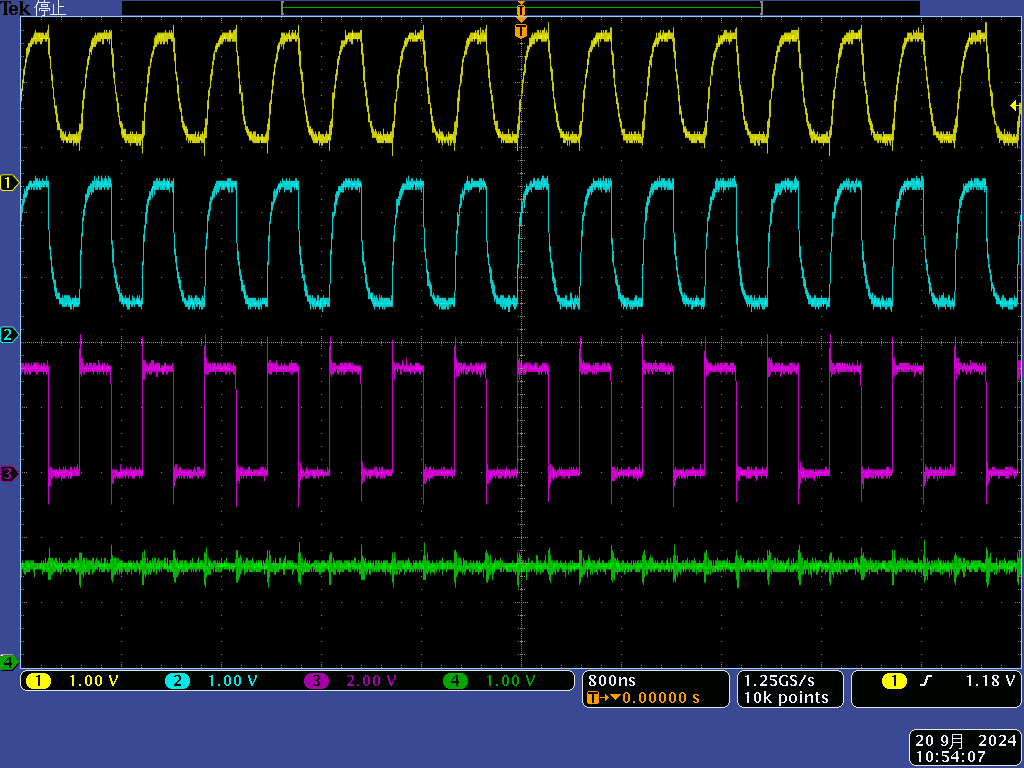

CH1:DIFF_OUT_N (prior to the coupling capacitors)

CH2:DIFF_OUT_P (prior to the coupling capacitors)

CH3:DIFF_IN

CH4:VREF

The DIFF_IN signal is a signal of about 1.4 kHz with 2 MHz OOK modulation.

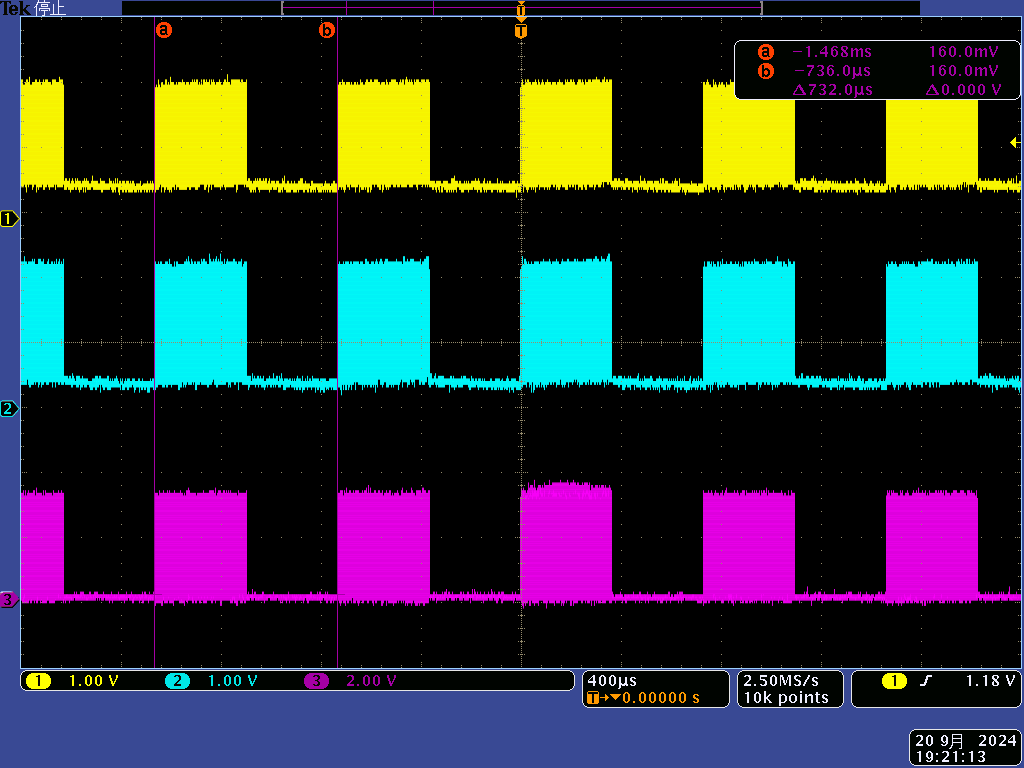

A waveform with a wider time range is attached.

CH1:DIFF_OUT_N (prior to the coupling capacitors)

CH2:DIFF_OUT_P (prior to the coupling capacitors)

CH3:DIFF_IN

Hi,

Thank you for sharing these details. I was able to look into our device and there is no reason there should not be a differential output. Could you confirm the scope setup is correct, and one channel is not inverted by any chance?

Best Regards,

Ignacio

Upon confirmation, there was no problem with the measurement method.

Also, suspecting IC failure, we checked with another board and found the same operation.

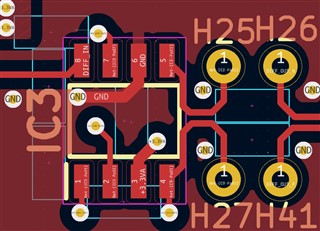

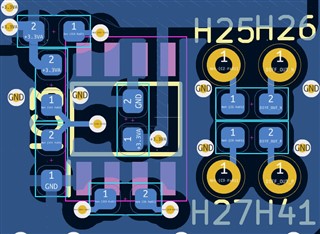

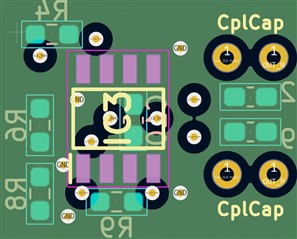

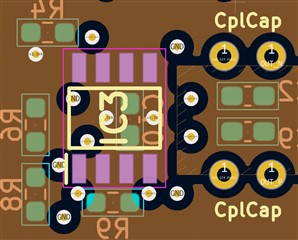

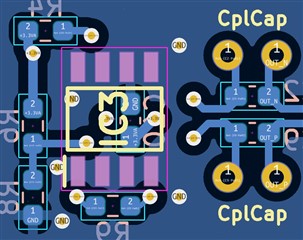

Are there any problems with the wiring?

In the previous prototype, the same circuit was used to output differential signals.

The difference is the input signal frequency and pattern wiring.

The previous prototype was a 4-layer board with the second layer being the GND plane and the third layer being the 3.3V power supply layer.

Hi,

Thank you for sharing additional information. I was able to look over the connections and it seems like everything is connected properly. The layout does have some non-ideal practices that we avoid to ensure the best circuit performance. However, I saw you mentioned the input frequency changing from the previous version. If you change the frequency, are you able to get two differential signals? I was also curious if you are able to put the device in a differential gain of 2V/V instead of the 4V/V the schematic showed. I would like to see if maybe overdriving is causing some kind of delay. You should be able to just short R9 to do this test.

Best Regards,

Ignacio