Other Parts Discussed in Thread: OPA2992, THS4551

Tool/software:

Dear TI expert,

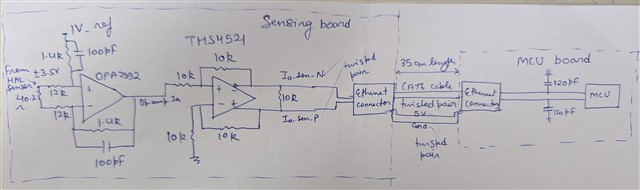

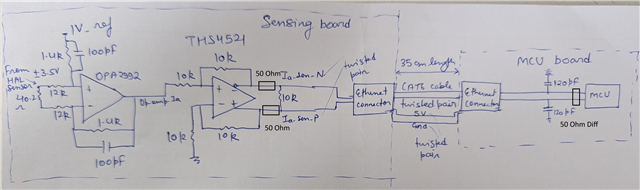

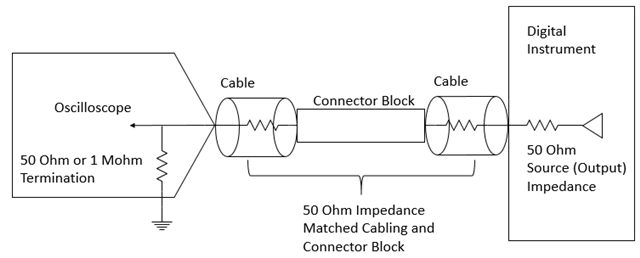

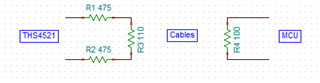

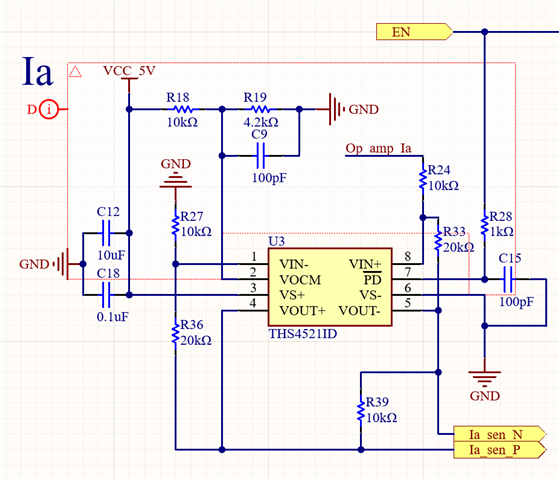

We are using THS4521 for converting single-ended to differential signal. Differential signals are going out of the board via ethernet cable to MCU ADC on the other board.

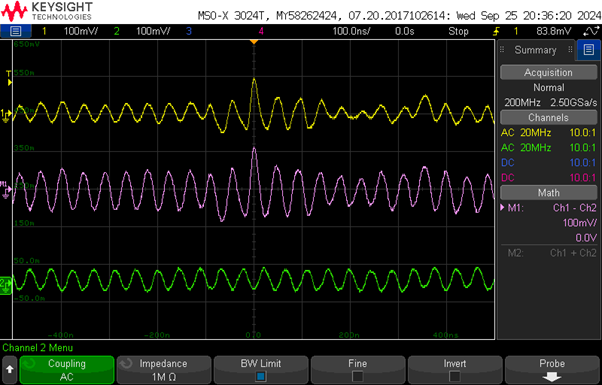

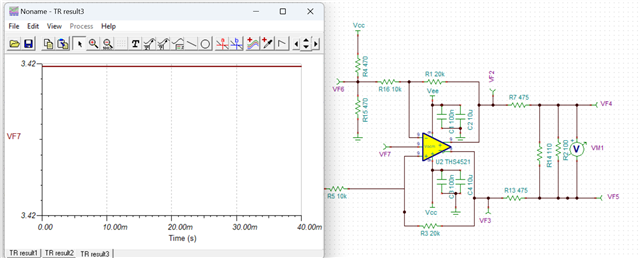

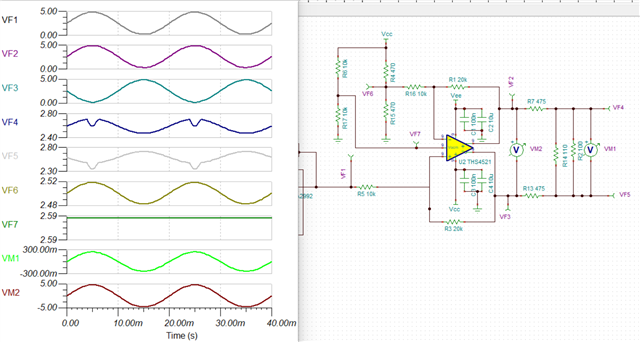

- MCU ADC configuration is in differential mode. But ADC output is having too much variation.

- On further testing with oscilloscope, without connecting the controller board, signals look much clean but as soon as the controller board is connected differential signals become bad. Especially the signal named Ia_sen_P, in picture below. Ia_sen_N is relatively very good.

Please suggest.

Regards,

Jitendra