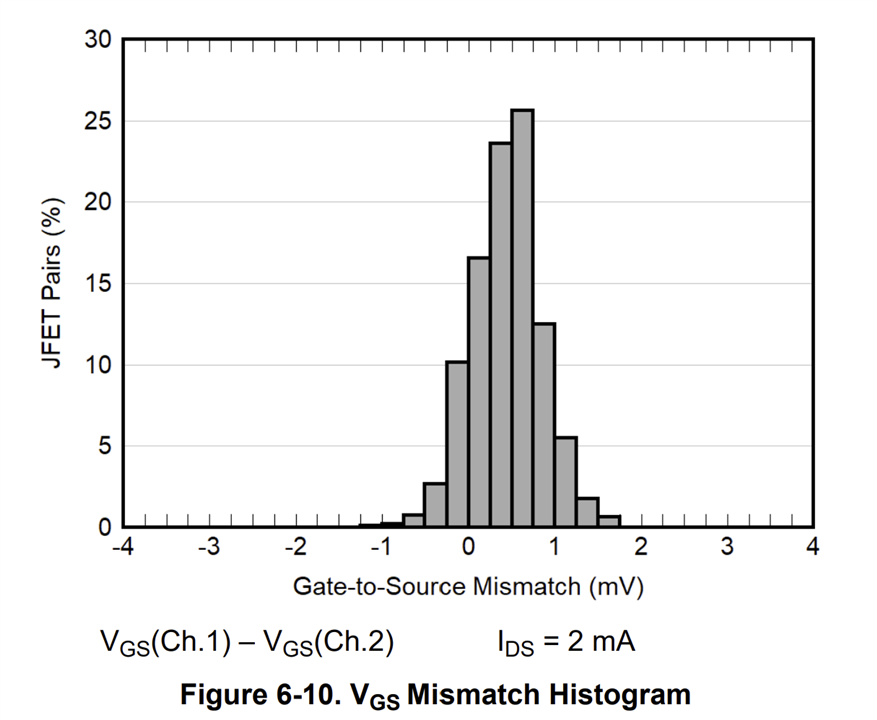

Part Number: JFE2140

Other Parts Discussed in Thread: , OPA1637, JFE150, OPA197, OPA1692, OPA202, OPA145, REF3425, REF3212, LM134, TINA-TI

Tool/software:

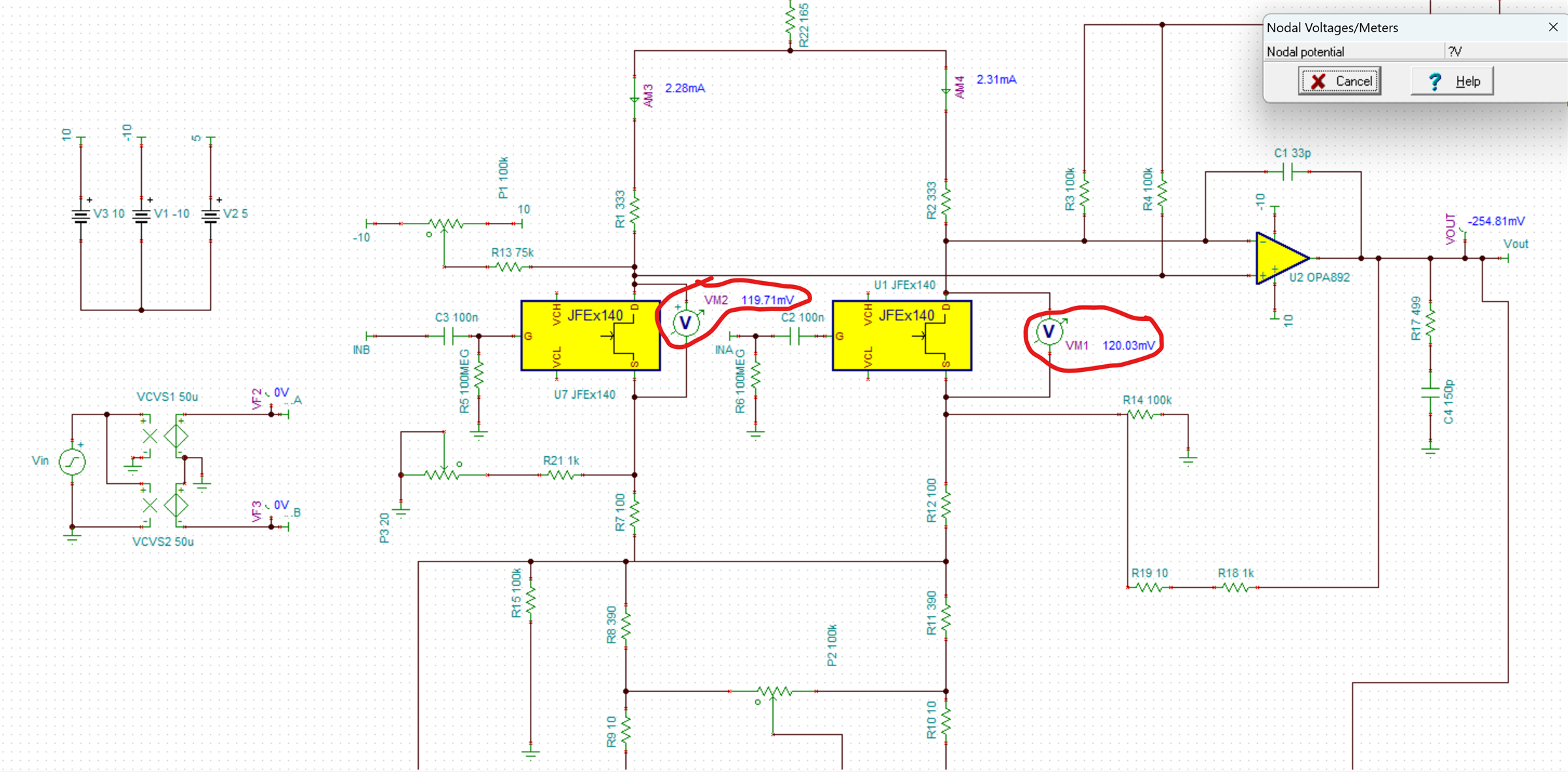

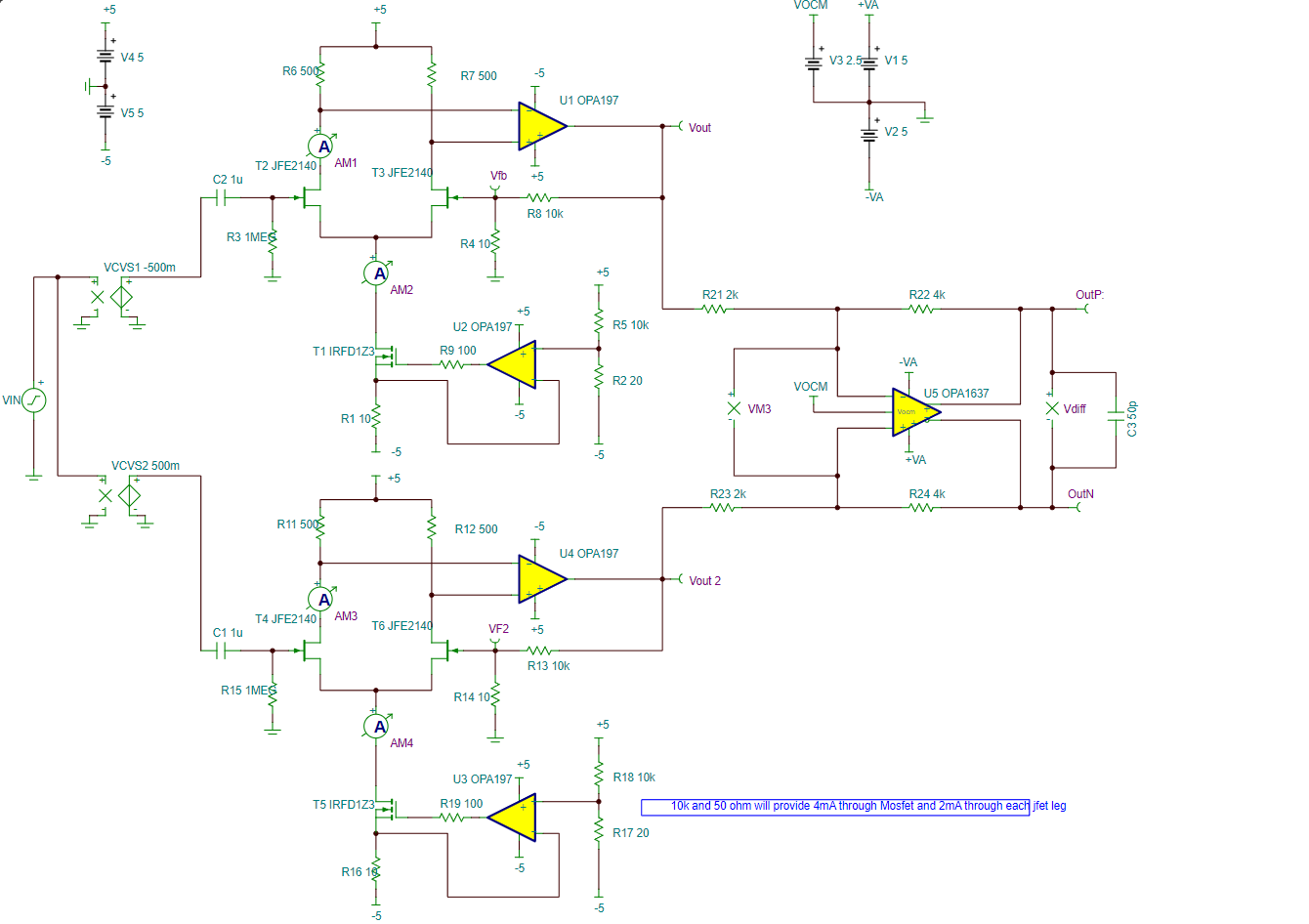

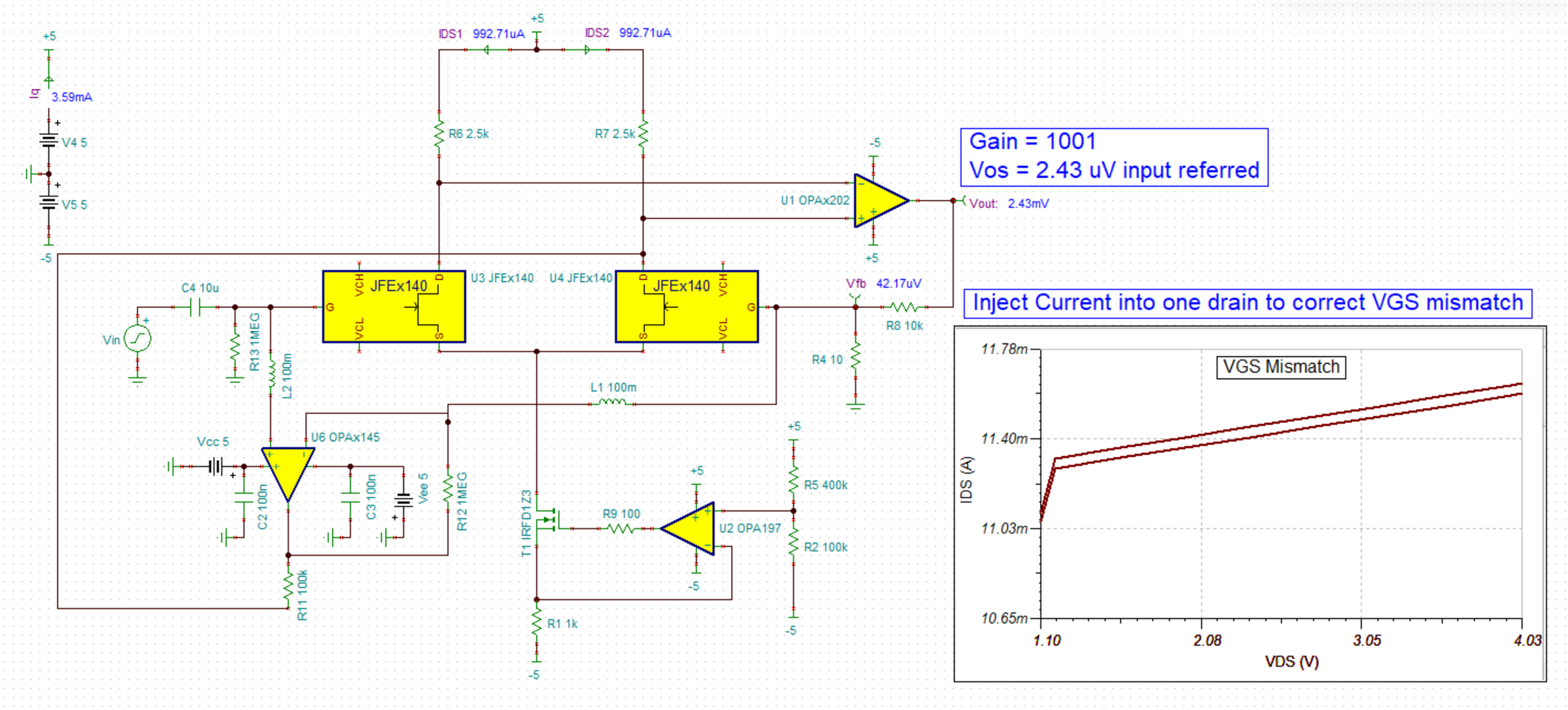

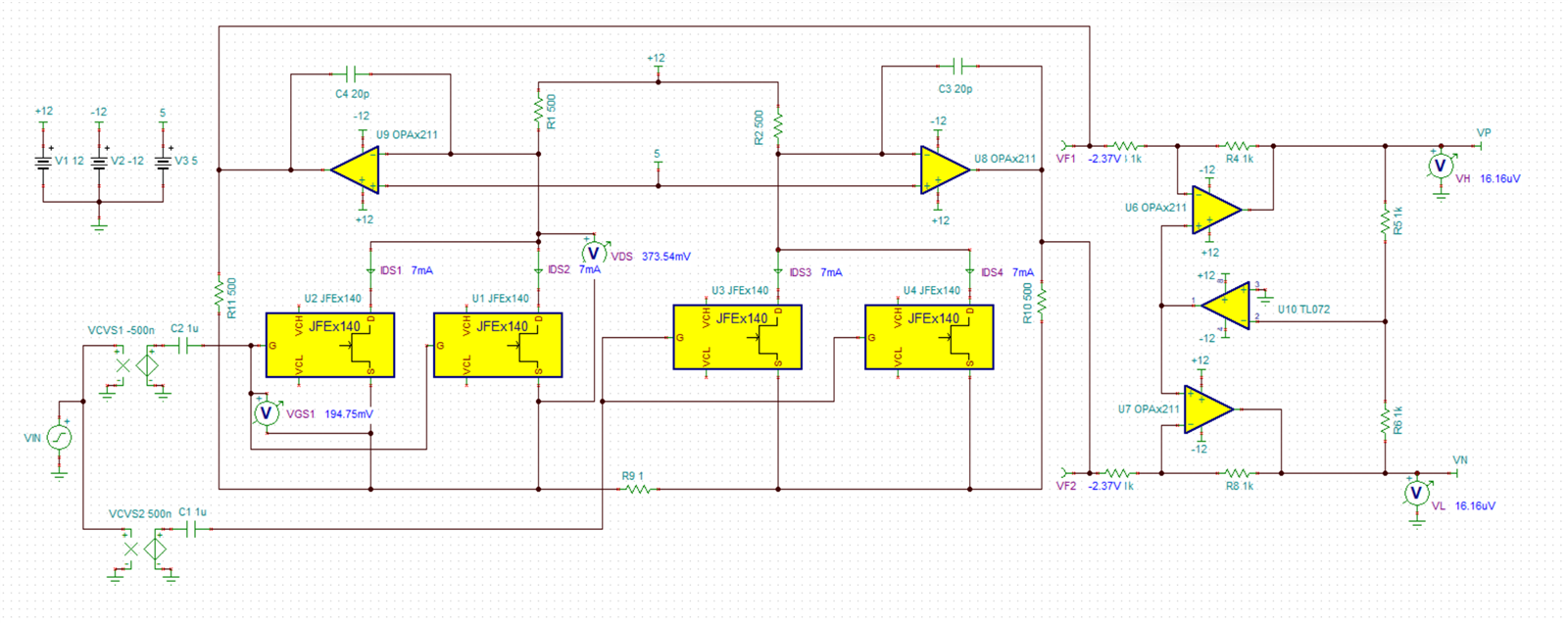

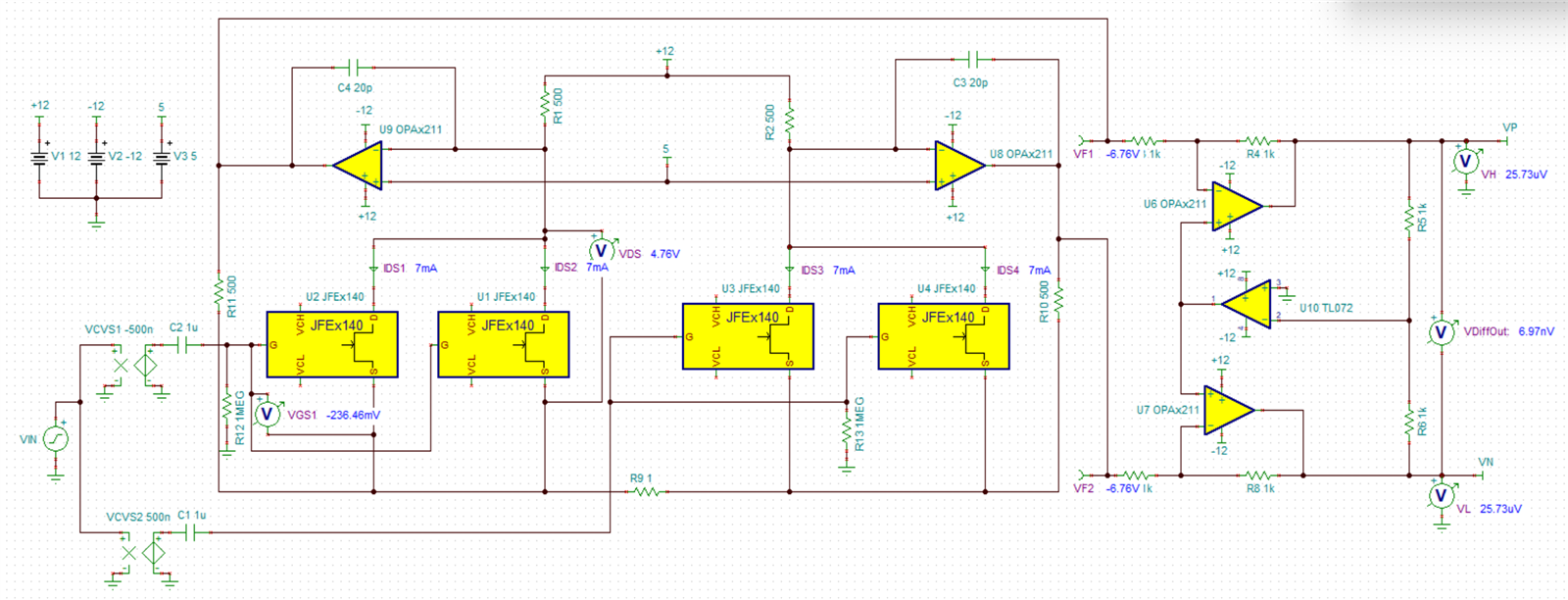

Hello TI,

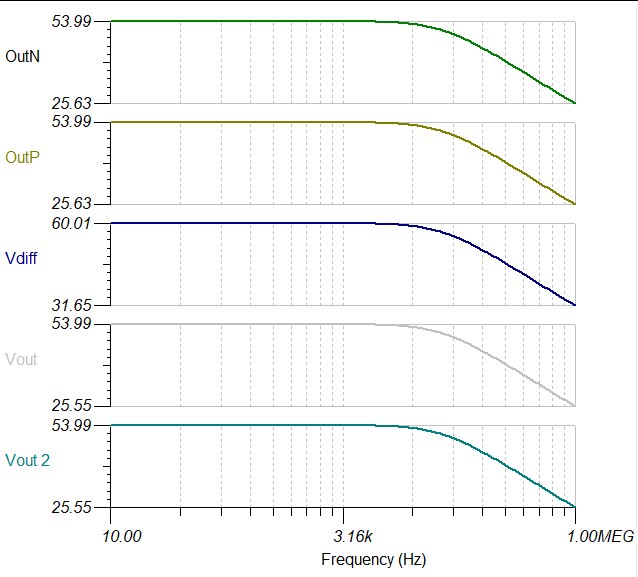

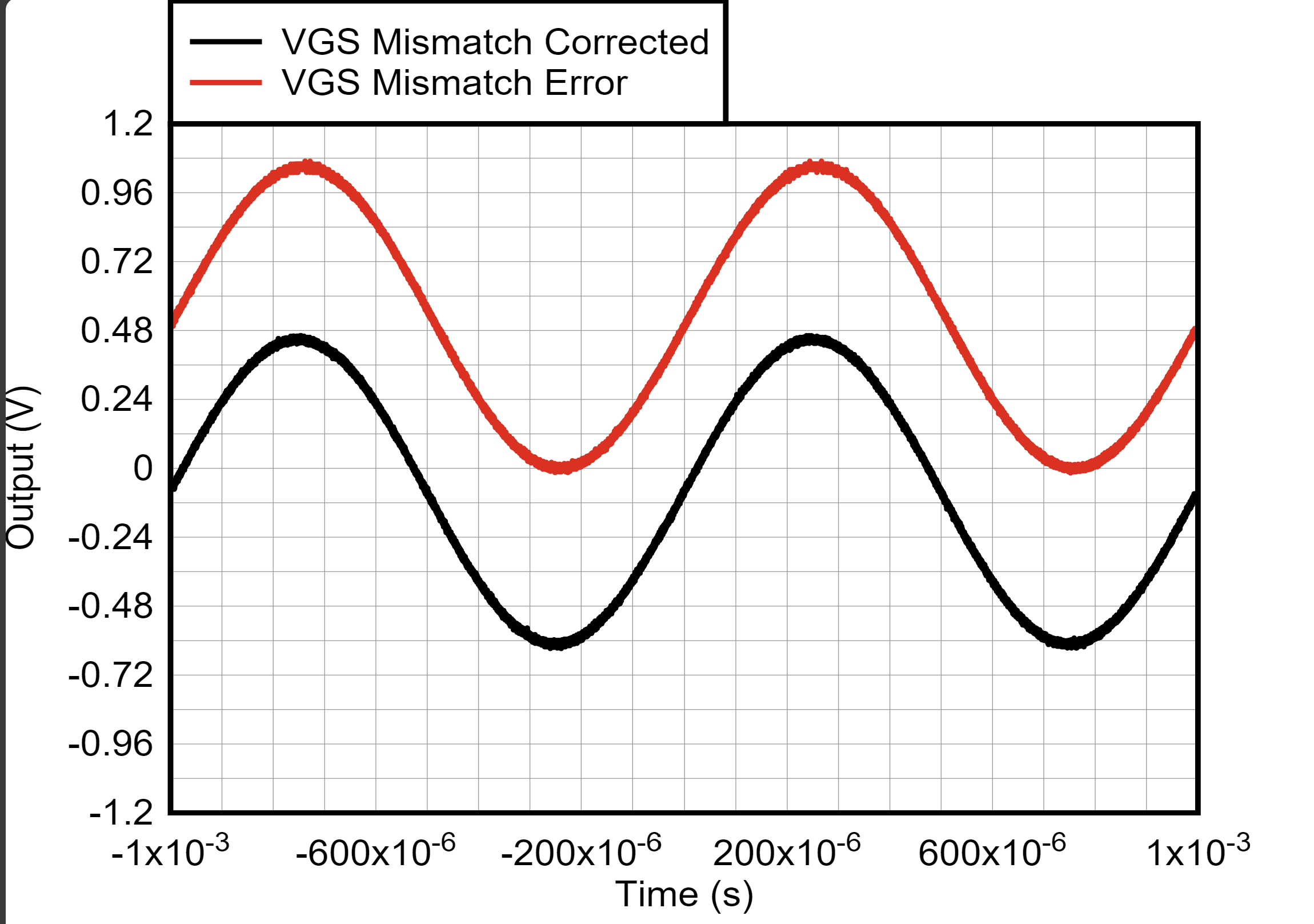

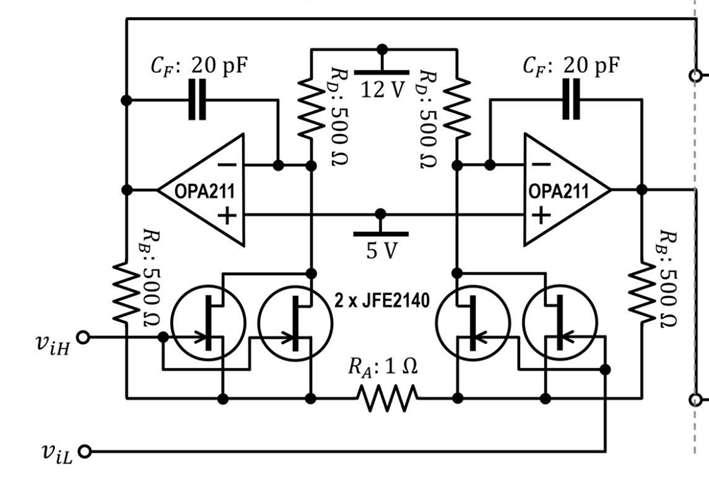

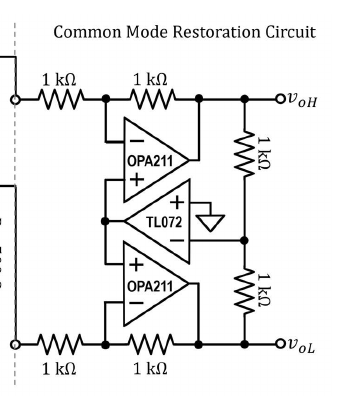

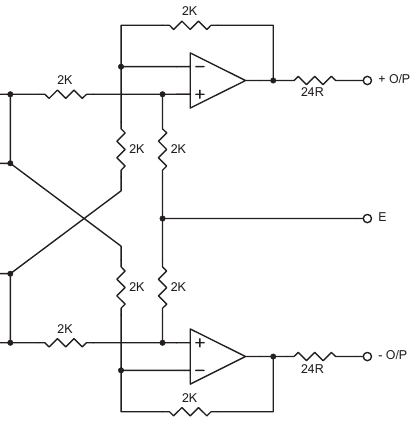

I am simulating a piezo transducer with capacitance of 66 nF and 100 K connected to this front end amplifier made for very low noise performance. The simulation results are horribly wrong. could anyone please let me know what is wrong in my simulation. Also I would like to calculate CMRR of this circuit from 10 Hz to 20 KHz. Please let me know. I intend to use it with gain of 10.

Please let me know what is the issue?