Other Parts Discussed in Thread: INA186

Tool/software:

Hi team,

Customer have a special test case for INA186-Q1 that would damage device. Would like to get some suggestions from your side.

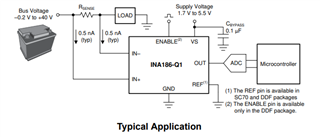

Take below block diagram as example, the test case is that VS and GND pin will be floated and then short IN- & IN+ to GND. Customer found INA186-Q1 was damaged after this test. The voltage they measured at VS and GND is about 13V. So IN+ & IN- are about -13V at this case. It is out of the ABS value in datasheet.

But this test case is required. So do you have any recommendations that INA186-Q1 can survive from this test? Or any other device can work?

Some thoughts from my side, please help check and let me know your thoughts.

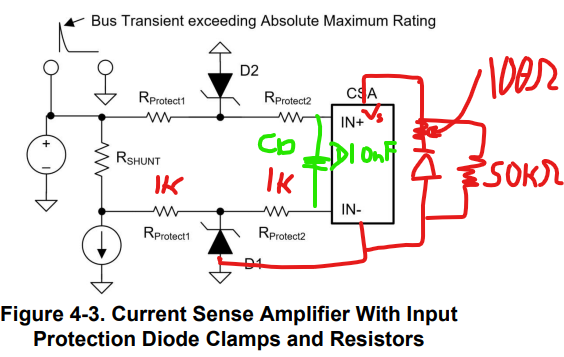

1. Add a current limiting resistor at both IN+ and IN-. To avoid the reverse current out of INA186 spec. But how to select the resistor value?

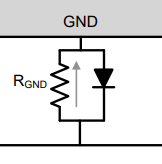

2. Add a reverse protection circuit as below, this is an example from our high side switch product.

Thanks!

Ethan Wen