Tool/software:

Hello,

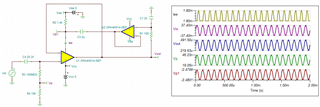

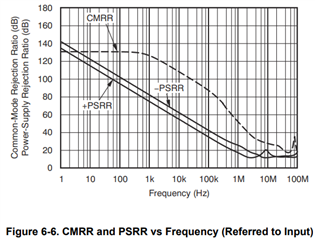

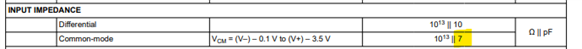

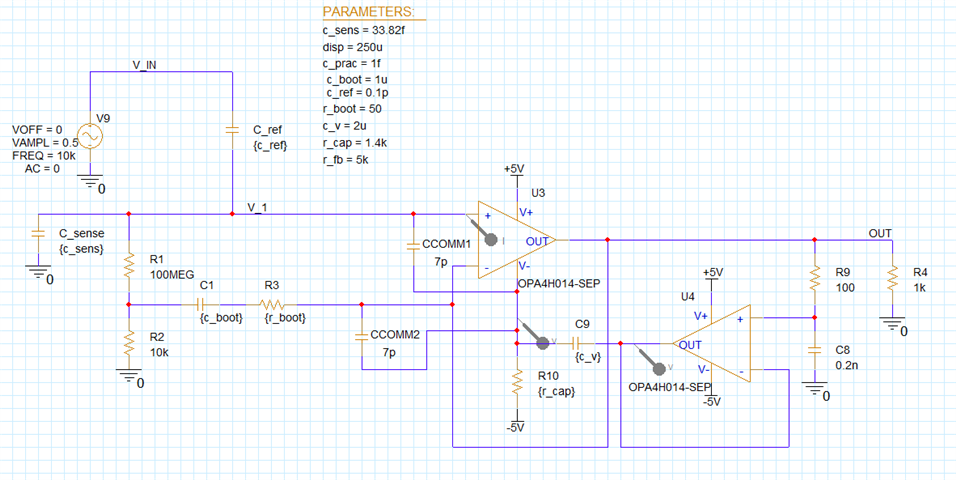

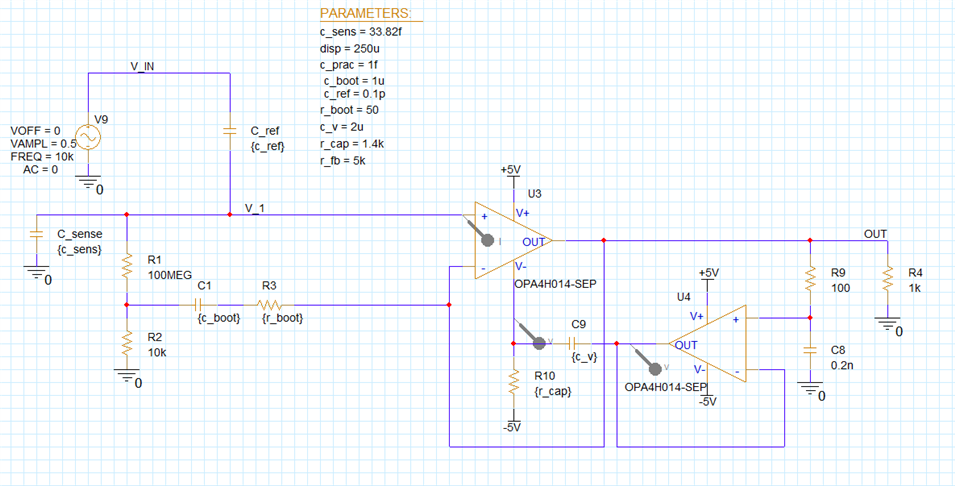

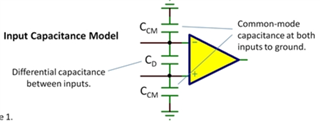

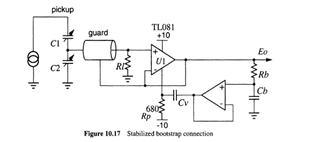

I am trying to use an front-end amplifier on a small capacitive sensor (0.033-0.1pF) for a space application. I like the OPA4H014-SEP because of its low bias current, current and voltage noise densities, and relatively low common mode input capacitance. In order to increase the sensitivity of the measurement in relation to the sensor, I want to employ a bootstrapped connection to the negative terminal of the op amp as shown below (using Rb, Cb, the unnamed op amp gate, Cv and Rp):

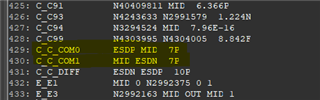

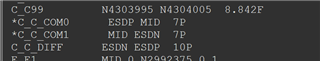

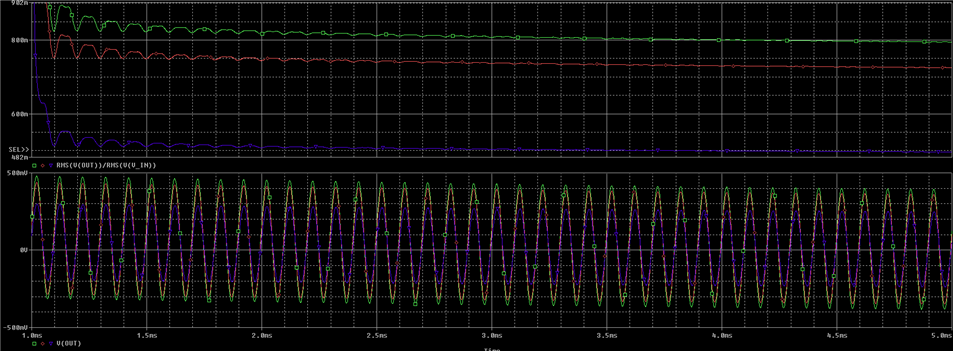

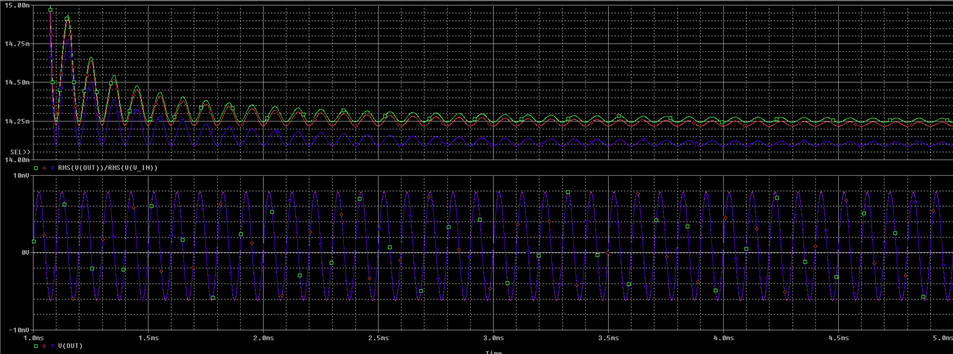

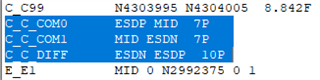

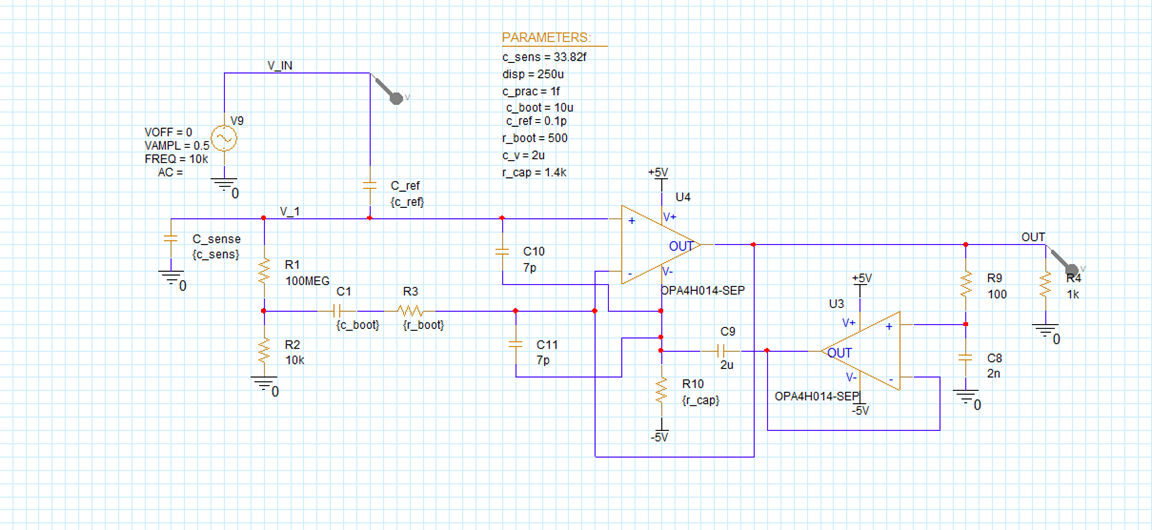

Based on what I was reading, this should effectively decrease the effects of the common mode input capacitance IF the common mode input capacitance is connected to the negative supply. I was looking at the PSPICE model for this part but was struggling to identify if this is the case for this part. When I run simulations with this topology, I do not get the intented effect. If I comment out the common mode capacitances on both inputs and add discrete capacitors of the same value to my simulation (with one end of the capacitor being on the input and the other being on the negative supply pin), I do get the intended effect. A picture of my current simulation set-up is shown below:

I want to know if this is a valid change to make for the sake of simulations, or if you have any alternate recommendations for bootstrapping out the effects of the common-mode capacitance. Alternately, if you know of a part with similar noise densities and input bias current but with a smaller common mode capacitance, that would be great. The input signal is 10kHz so the bandwidth just needs to be enough to support this. Thanks!