Tool/software:

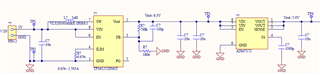

Vin: I created a circuit that boots from 5V to 6.3V and converts it to 5V with a regulator, but when I connect a 100mA load, Vout drops to 5.3V.

Why can't it maintain 6.3V?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hi Hori,

Can you catch a waveform of the unexpected Vout drop. Please probe Vin,Vout,SW pin in the same screen.

Best Regards,

Travis

Hi Travis

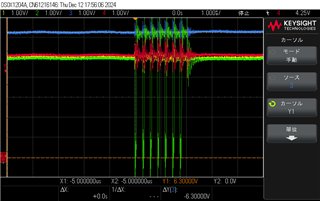

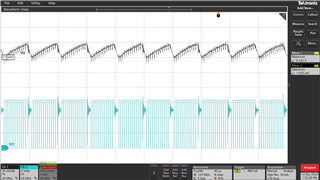

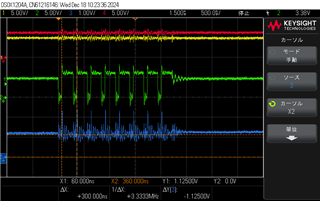

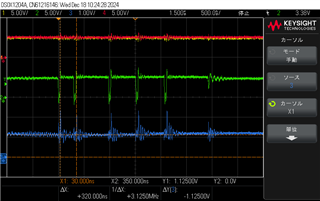

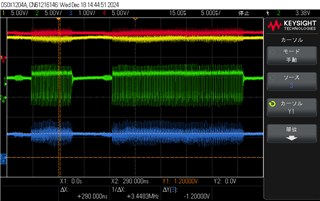

The waveforms are Ch1: Vin, CH2: SW, CH3: Vout, CH4: regulator, 5V.

The first panel is at no load

The second panel is at 30mA load

The third panel is at 100mA load

Vout is 6.3V at no load

6.0V at 30mA load

5.3V at 100mA load

The sine current is set to 1500mA.

Hi Hori,

Thank you. I'll test on my bench and check the difference.

Best Regards,

Travis

Hi Hori,

I tried the same condition on EVM and it works normally. Can you catch SW, Vout, FB and ILIM pin voltage on your bench and catch waveform again. Open 20MHz band width limit on all channels to reduce noise.

Best Regards,

Travis

Hi hori,

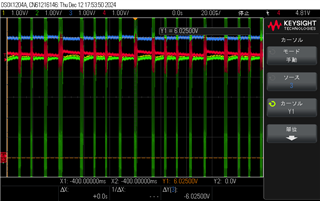

My waveform is captured with 100mA CC load.

The Vout is 6.3V as expected.(the black curve is Vout with 6.3V offset )

Best Regards,

Travis

Hi hori,

The IC current limit does not support 1.5A load. Your waveform shows the IC is still in light load condition. So I suggest focusing on previous waveform. Can you catch SW, Vout, FB and ILIM pin voltage waveform on your bench?

Best Regards,

Travis

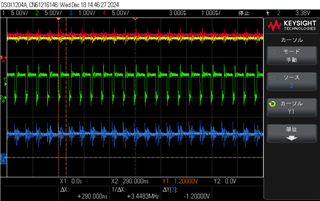

Hi Travis

I will send you the waveforms.

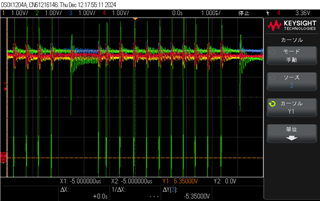

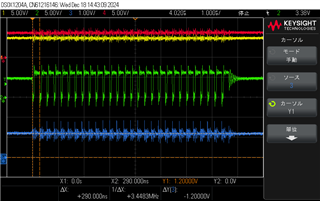

CH1: Vin

CH2: SW

CH3: FB

CH4: Vout

The first one is no load, the second one is a 100mA load.

When I connect the load, it seems like the PFM modulation is not working properly.

no load 100mA load.

Hi hori,

The modulation circuit is working normally. The Toff becomes longer because Vout drops very close to Vin and volt-second balance is hard to be established. I think the root cause is from the FB divider part. The FB voltage is still around 1.2V on the second waveform when Vout drops to 5.3V. According to the divider ratio, the FB voltage should be 5.3V*180k/(768k+180k)=1.006V while the waveform shows FB is above 1.125V line.

Can you remove feed forward capacitor and try again. Or is there some other circuit around FB divider that's not shown in the schematic.

Best Regards,

Travis

Hi Travis

After removing the 100p capacitor next to the 768k,

I was able to maintain 6.3V even with a load of 100mA.

However, when the load is increased to 300mA, Vout drops to about 5.9V again.

Why is that?

I will also show the waveforms.

As shown in the circuit diagram, there is a step-down circuit after the step-up circuit.

An electronic load is connected beyond that to pass the load current.

At no load(Vout:6.3V) Load of 100mA(Vout:6.3V)

Load of 300mA(Vout:5.9V)

Hi Hori,

Honestly, I cannot tell why your divider is not dividing Vout by the expected ratio. I'm applying the same 768k, 180k and 100pF divider as your schematic and the output is correct as expected. Can you share layout so that I can check it? Also, please apply an EVM and see whether the same IC works normally on EVM.

Best Regards,

Travis

Hi hori,

Switching regulators are very sensitive to parasitic inductance on layout and cannot work normally without proper layout. Please apply for an EVM if you need to evaluate the performance.

TPS61252EVM-667 Evaluation board | TI.com

EVM is a evaluation PCB consists of our IC and external components. Please apply a EVM.

Best Regards,

Travis