Other Parts Discussed in Thread: PGA855, INA159, INA500

Tool/software:

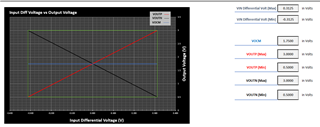

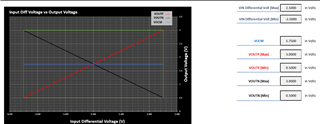

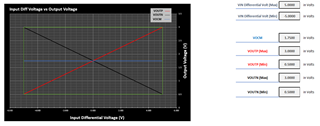

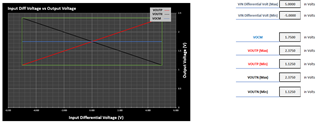

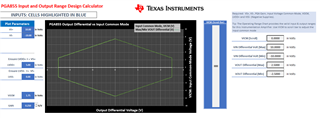

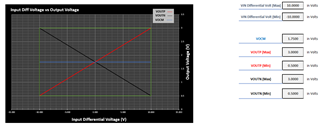

Hi, I need to design an analog front-end for differential signal acquisition. The ADC can be 1MSPS and powered with 3.3V or 5V, Vref=3V or 4.096V. The input ranges has to be +/-0.1V, +/-0.5V, +/-1V, +/-2V, +/-5V. We can use for example a programmable gain istrumentation amplifier driven by micro as first stage with input protection for overvoltage. Can you give us support for the chain design using your products? Can you suggest the best solution/architecture? Thanks