Tool/software:

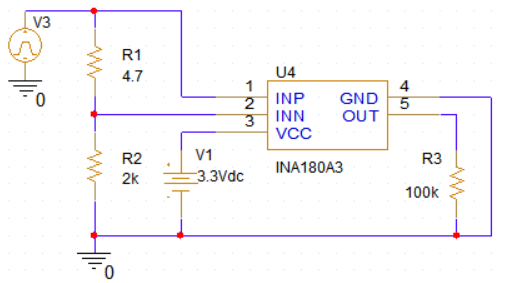

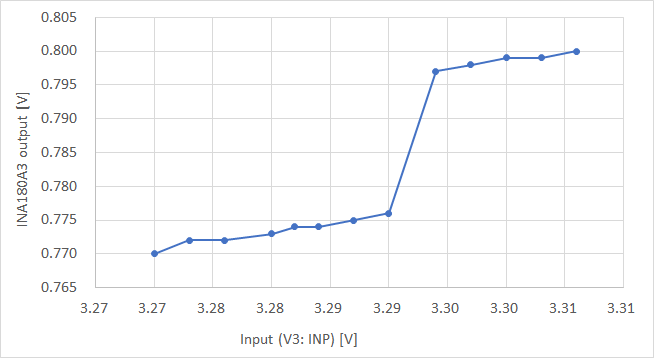

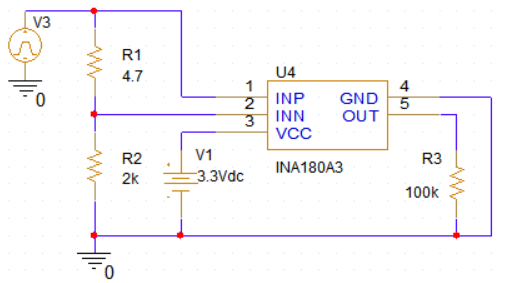

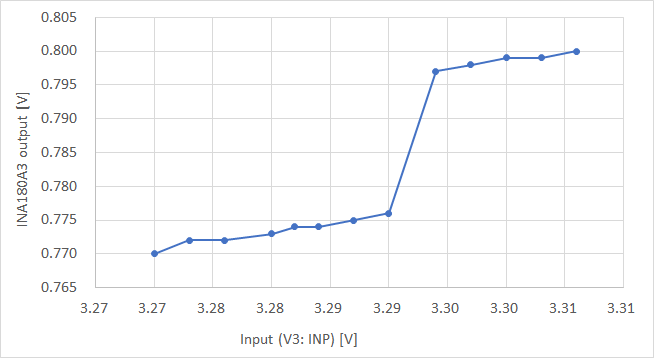

図に示す回路で電流を変換すると、グラフにステップが発生しました。

図に示す回路で電流を変換すると、グラフにステップが発生しました。

この現象は、このICの設計から想定されていたものなのでしょうか?

段差を減らしたり、なくす方法があれば教えてください。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Tool/software:

図に示す回路で電流を変換すると、グラフにステップが発生しました。

図に示す回路で電流を変換すると、グラフにステップが発生しました。

この現象は、このICの設計から想定されていたものなのでしょうか?

段差を減らしたり、なくす方法があれば教えてください。

Hey Takeshi,

Welcome to the forum and thank you for your question.

I can’t decipher your text, but I can see what’s happening in the circuit.

This is not a model issue or an effect of gain non-linearity.

The issue is the increase in input bias current (IB)(~58uA change) when Vcm exceeds Vs. Given you have around a 4.7 Ohm shunt resistance, the offset from IB (Vos_IB) will increase by 270 uV. And this is gained up to 27mV at output, which is exactly what you’re seeing.

See Figure 7-20 to understand this device behavior.

Sincerely,

Peter

Hi Peter,

Thank you very much for your quick answer.

It was very helpful.

I'm afraid I typed it in Japanese.

Here is the English translation for your reference.

-------------------

When the current was converted by the circuit shown in the figure, a step occurred in the graph.

-> As you understand.

Is this phenomenon expected from the design of this IC?

-> Already answered.

Please tell me if there is a way to reduce or eliminate the step.

-> I would like to use the current circuit, but if you have a good idea, please let me know.

Sincerely,

Hey Takeshi,

No problem. If you want to eliminate/reduce this step, then you need to decrease shunt resistor (R1) and then switch to higher gain variant (INA4181A4).

Or you could move the amplifier to the low-side of the circuit.

Best,

Peter