Tool/software:

Hello

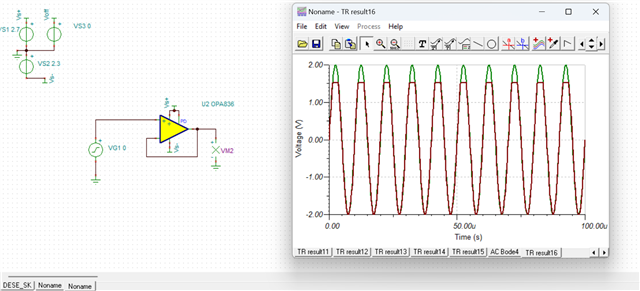

I'm simulating a design using two OPA836, the first one used as a difference amplifier, which feeds into a Sallen Key cell.

The output of the second stage saturates at a much lower value than the first stage, and much lower than the supply voltage.

This happens only on the positive swing, on the negative swing the sallen key output reaches correctly the negative supply voltage.

I tried simulating it both with Pspice and TINA TI, same result.

It shows the same behaviour also if I simulate just one OPA836 used as a buffer: if I place a series resistor in the input path, and this effect is mitigated if i place a resistor in the feedback path(gain stil remains 1)

I'm failing to explain it since, according to the datasheet, the input impedance should be quite high, so a series resistance should not have an impact.

In fact it seems that there's a current flowing into the OPAMP inputs that causes the voltage drop.

I also tried replicating it testing a real circuit but I didn't get the same behaviour.

Here's the simulation file

Mattia