Tool/software:

Dear TI-PSPICE team

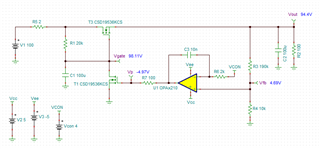

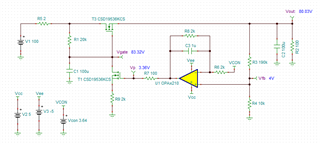

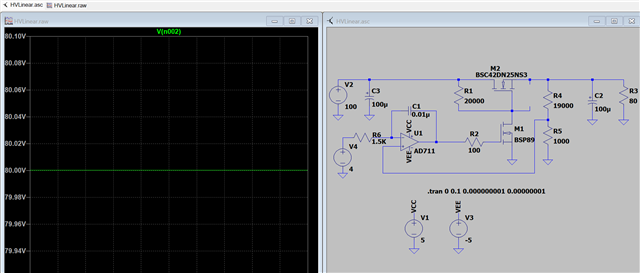

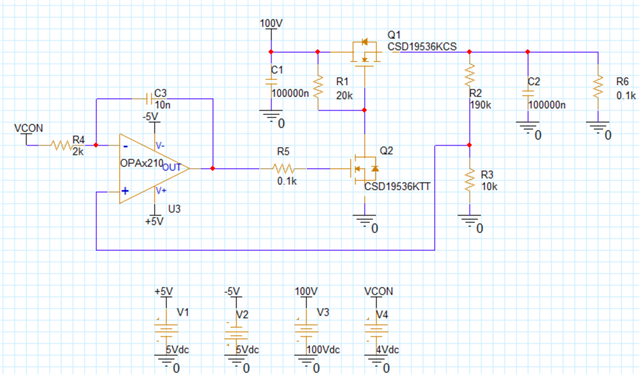

I use TI-PSPICE to simulate a high voltage discrete linear regulator for my customer. however, I meet converge issue even I update simulation conditions. could you please help to solve converge issue? my schematic as below figure shows. also attached my schematic file in here for debug the issue. thanks a ton!

regards,

Bill