Other Parts Discussed in Thread: LM339, LM393

Tool/software:

Dear Experts,

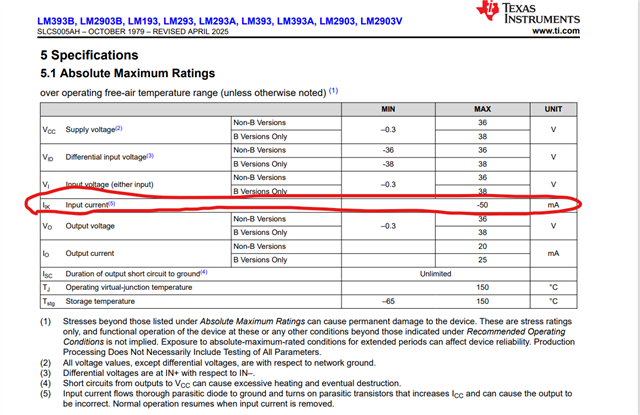

We are evaluating the operational amplifier LM193DR and would like to know the maximum reverse current that the chip can withstand in the event of negative input. Is this the IIk value(-50mA) in the reference specification? At this current, how long can the chip withstand without failure? Do you have any data to provide? Thank you~