Tool/software:

Hi,

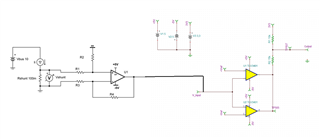

we use TLV3402 in dual window comparator configuration for detection of overcurrent in both directions.

Comparator is powered in bipolar configuration +/-5V but output should swing between 0 and 3.3V. Voltage divider is implemented on the output as level translator.

The input signal for comparator is output of the difference amplifier.

We assume the voltage translation hasn't been implemented properly, but we want to share some observation. Actually, we need help to figure out, why this is happening here.

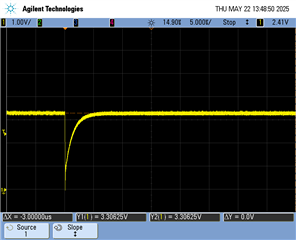

No current is flowing through the shunt resistor and TP507 is pulled to 3.3V. So, if we want to check voltage levels of test points TP507 and TP505 against GND using digital multimeter, we have observed short voltage drop on the TP507.

We connected the oscilloscope probe tip first, and afterwards the digital multimeter in order to record the voltage drop.

However, if we do the same on the TP505, nothing happens, or no voltage drop is present. Actually, this drop on TP507 can be provoked if you shortly connect 1nF capacitor or 10Meg resistor, or any other strange body that has enough absolute self capacitance.

If we add capacitor 1~10nF between TP507 and GND, no voltage drop can be observed anymore.

Please find attached schematic representation and waveform.

Could you help us to understand what is going on here and why?

How the level translation on the output could be improved?

Regards

Josko