Other Parts Discussed in Thread: TINA-TI, TLV9351

Tool/software:

Hi,

I'm trying to add right leg drive to my design, and have a couple of questions. I get the concept well, but most of the papers/docs/articles/videos I have seen online from multiple sources don't explain all of the components or how I would calculate appropriate values, so I have a few unknowns still.

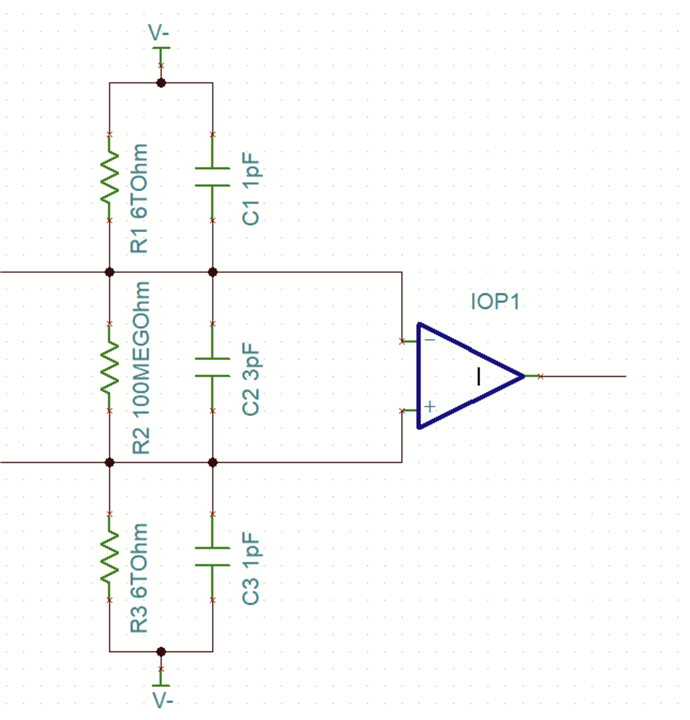

Note: a lot of walkthroughs/derivations of DRL take the common-mode signal from the output of the two buffers, as this is enough to demonstrate things conceptually. I'm not looking to make my own INA from discrete opamps, so, all of the below applies to implementing DRL using the common-mode signal from the external gain resistor.

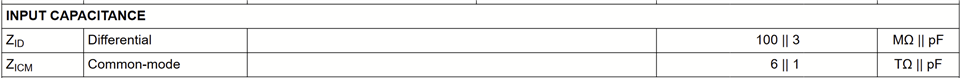

1) Gain resistor network.

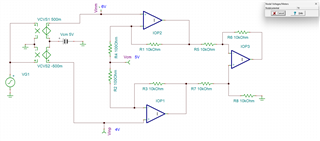

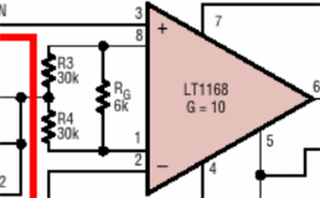

Some designs I see tap the common-mode signal across two gain resistors:

Other designs add a third in parallel with these two:

Could anyone please explain the reason for this third resistor? Is it just for component matching/tolerance, or does it relate to having a buffer or not before the inverting amplifier? How should I select appropriate values for the downstream amplifier and for the appropriate gain of the INA?

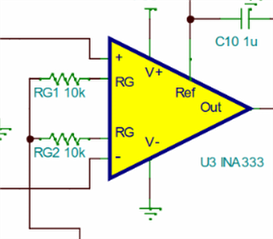

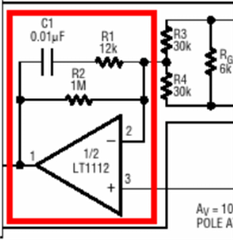

2) Use of Buffer

Some designs feed the tapped common-mode signal straight into an inverting amplifier:

Other designs have a buffer in front of the inverting amplifier:

What are the advantages of this? Is it to prevent any instability in the inverting amplifier from entering back into the common-mode signal in the INA?

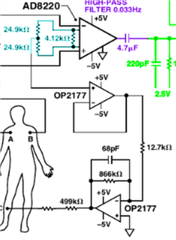

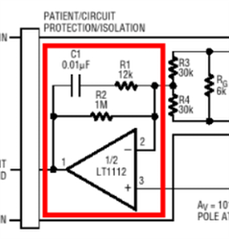

3) Filtering

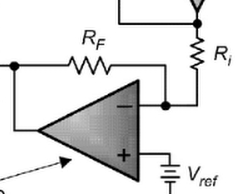

Basic designs just use a resistor network for setting the gain of the inverting amplifier and a short-protection resistor:

Others include a lowpass filter and a stabilising filter:

I see others using a high-pass filter(?) too:

My basic understanding is that the filter is to reject high-frequency noise that's outwith the signal passband anyway. And also because most INAs have lower CMRR above ~10-20kHz, so we should just neglect that range. If I am filtering this on the amplifier inputs anyway, then I shouldn't be trying to feed that back in.

Should the corner frequency of the lowpass be roughly matched to my input filters? I.e., the -3dB of my RFI filter is about 45Hz, as I am working with EEG and anything above this is out of range for my application. Is the idea that I should filter out roughly the same frequency range on the inverter?

Then, I assume that the stabilising section is to prevent resonance in the feedback network - we need to dampen the signal as we're using negative feedback so an impulse in the common-mode signal at the inputs could cause the DRL circuit to oscillate violently back and forth. Is there a guide on how I could calculate appropriate values for this, or can I use a generic reference on attenuating negative feedback loops when using opamps? I've seen the concept of resonance in other contexts before, but not specifically in electronics, so, I think I could probably look up a general circuit template and work with that - but soe of it might go over my head a bit and I'm not sure if there are special considerations I need to take into account here.

Would anyone be able to help me or point in the right direction on these points please? Or know any resources on how to choose the specifics of implementing an RLD subcircuit? As I'm finding a lot of guides going over the concepts, but at my low level of electronics understanding, I'm struggling a bit to translate this into a specific schematic that I can use.

Thank a lot for your help!!