Tool/software:

Hello.

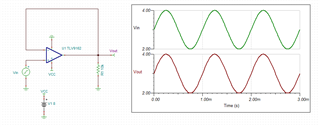

I am instantiating two unique opamps, obviously with different models, into Cadence to do a spectre simulation.

In general pspice simulations work well in Cadence.

BUT the two TI models do not uniquify their sub circuits...

One example, both spice models have something like (just showing definition)

* FEMT - INPUT CURRENT NOISE IN FA/RT-HZ

.SUBCKT FEMT_0 1 2

And clearly spectre throws an error because it has been defined twice....

There are about fifteen of different subckts and I could edit them and uniquely everything, but there must be a better way....

Regards

Phil