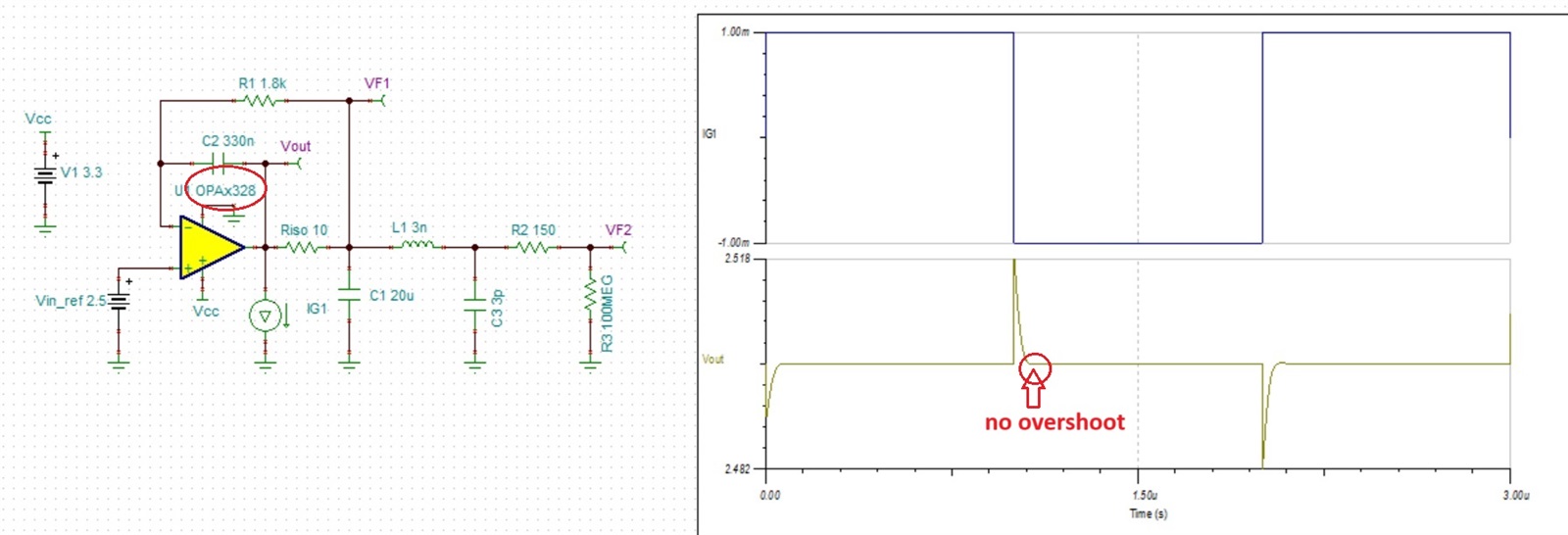

Other Parts Discussed in Thread: OPA350, THS4281, OPA333, OPA328, TINA-TI

Tool/software:

Hello TI support,

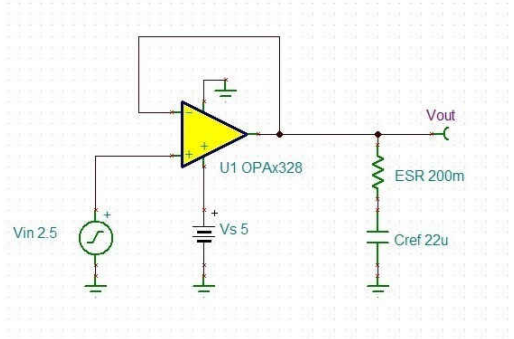

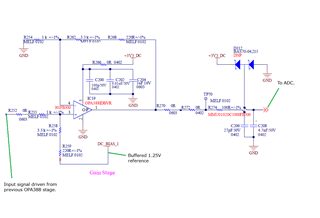

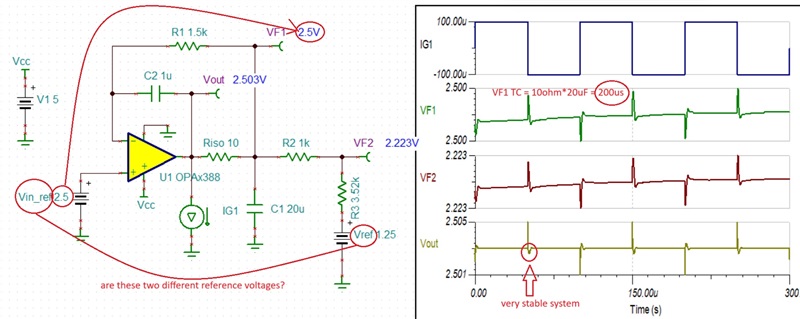

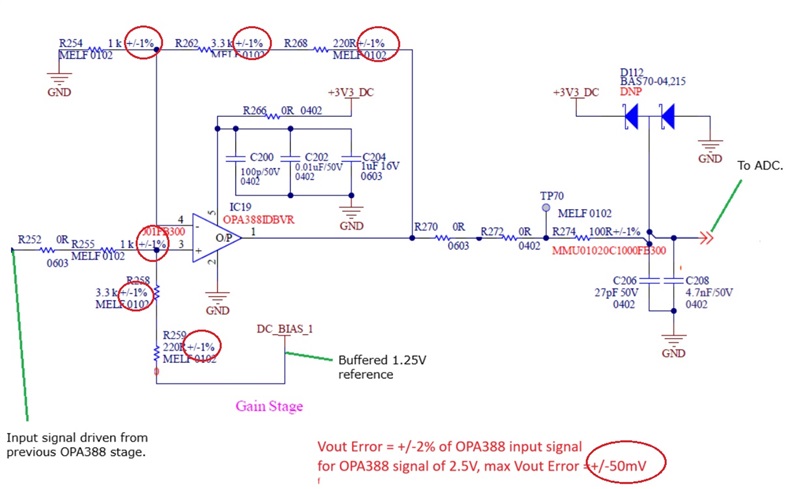

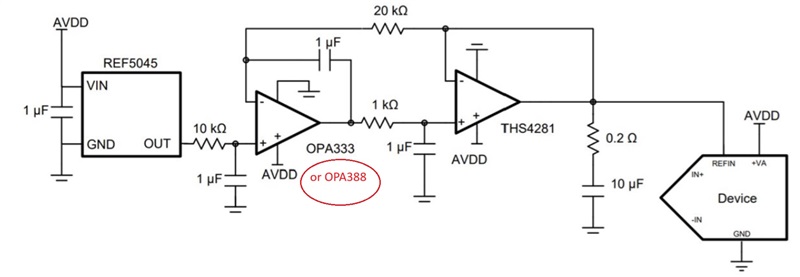

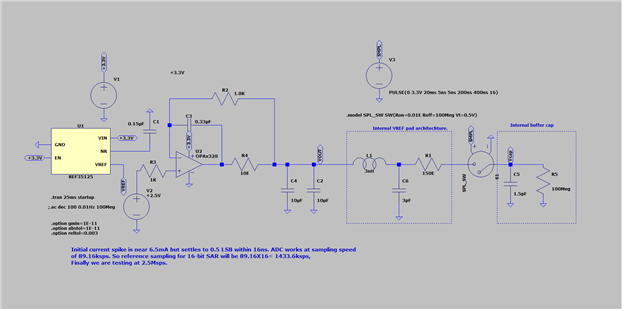

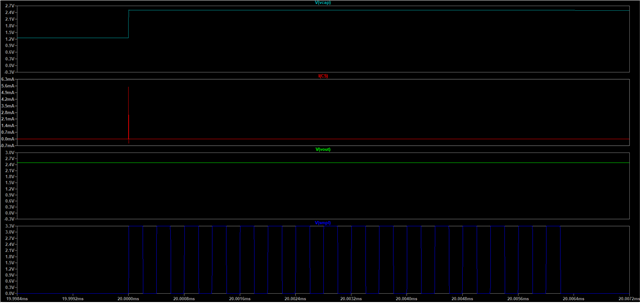

Can we use use OPA388 as reference buffer for 16-bit SAR ADC with 2X 10uF tantalum capacitor as its output load? If not, please suggest suitable precision opamp supporting 3.3V supply range.

Regards,

JK