Tool/software:

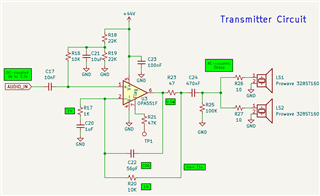

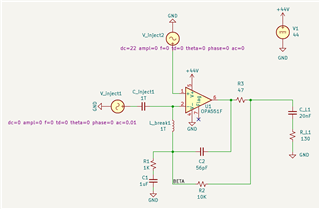

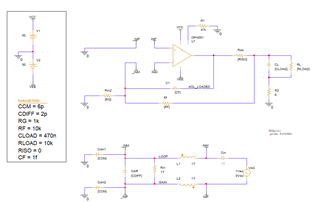

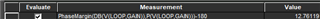

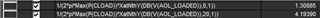

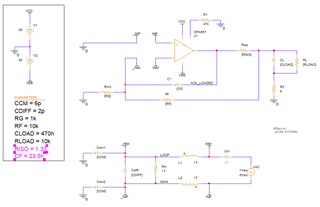

Hello, I'm working on a design to drive two piezo transducers in parallel using an OPA551. I've been trying to assess phase margin using a "break the loop" method in SPICE to ensure it will remain stable with the highly reactive load, and I'm having problems getting to a sane result. Attached is my actual circuit, and then my simulation circuit where I'm attempting to break the loop for AC analysis. I believe the analysis suggests 85 degrees phase margin, however if I increase the load capacitance to a ridiculous value like 10uF, it remains the same, so I believe my sim circuit is wrong. Can I please have some assistance assessing phase margin for this circuit, and also feedback on why my simulation circuit is incorrect? I'd like to use it to assess the best isolation resistor value to use. I have watched a couple of TI videos on the topic but am still struggling to get a simulation result that makes sense to me over various Riso and load conditions.