Tool/software:

Dears,

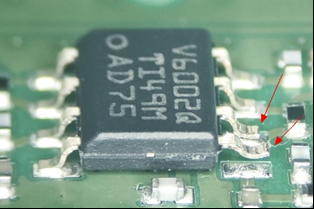

The model used by the customer is TLV6002QDRQ1, packaged in SOIC-8, as shown on page 29 of the specification. As discussed over the phone, please refer to the information on the coplanarity dimensions that conform to the semi-circular shape in the image below. Engineer Sun, Wang Shuai, the SMT placement has caused the pins to lift, leading to poor placement quality.

The coplanarity of the transistor lead material 31030452 exceeds the limit, leading to poor soldering after reflow; defect ratio: 9/8100 = 0.1%

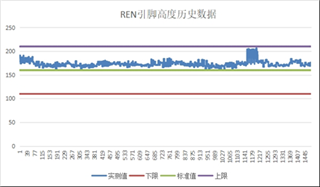

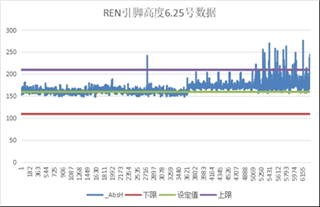

Using 3D AOI to compare the pin warping height between the early and recent stages (pin thickness 150μm, coplanarity tolerance 100μm; a height exceeding 250μm is considered an excessive height according to 3D AOI measurements, with some materials in the process having a measured height exceeding 260μm), it has been found that the recent pin height data is unstable. Please provide feedback to the supplier to analyze and confirm the reason.

Given the unusual background mentioned above, the client hopes we can provide the following information:

1. Is TI's factory 100% monitoring co-planarity? How is it being monitored?

2. Please confirm the co-planarity standards.

3. The co-planarity control standard is <0.1, please confirm if this can be met;

4. Investigate the causes of flatness discrepancies between different batches?

Many thanks,

Arabella