Other Parts Discussed in Thread: OPA189, INA849

Tool/software:

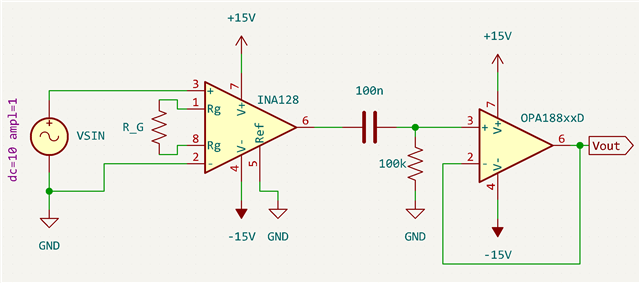

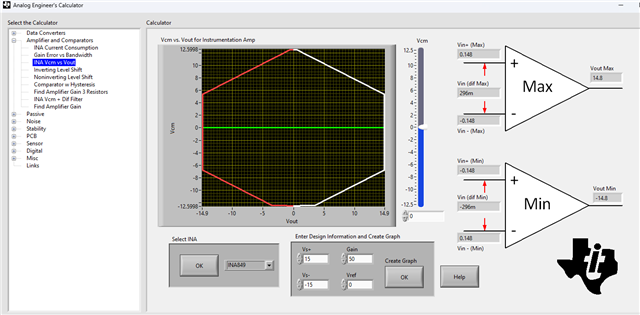

Hello, I have a question regarding the circuit presented in article TIDU990. This is the circuit in question:

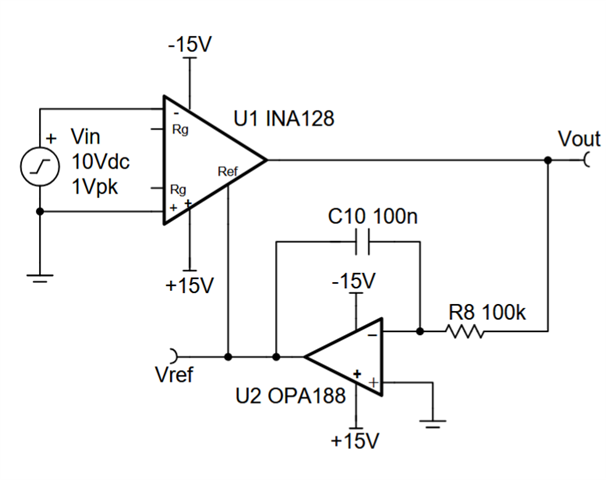

The circuit is presented as a superior alternative to putting RC highpass filters at both inputs of the instrumentation amplifier, and the advantages are discussed. My question is: what are the tradeoffs to, instead of feeding the integrator into the REF pin of the inamp, following the inamp with an active HPF with the same RC values of the integrator. For clarity, here is the circuit: