Tool/software:

Hi team,

Customer is using TAS2505. If the sampling rate is 22.05 kHz and the bit depth is 16 bits, how should the audio MCLK and BCLK be set? Can you provide the corresponding PLL register settings?

Thanks

Xiaoxiang

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Tool/software:

Hi team,

Customer is using TAS2505. If the sampling rate is 22.05 kHz and the bit depth is 16 bits, how should the audio MCLK and BCLK be set? Can you provide the corresponding PLL register settings?

Thanks

Xiaoxiang

Hey Xiaoxiang,

BCK= FSYNC * number of channels * number of bits per channel.

Right now, the customer is able to calculate the BCK frequency based on FSYNC = 22.05KHz and number of bits per channel = 16 bits.The number of channels would be based on the i2s signal the customer is feeding into IC. All these values would determine the BCLK. MCLK isn't needed in these types of situations. PLL in this IC is usually in an auto-detecting mode. There is also the option of on-chip pll the chip provides.

Regards,

Ore.

Hi Ore,

The TAS2505 requires setting up the PLL, could you provide the corresponding register configuration?

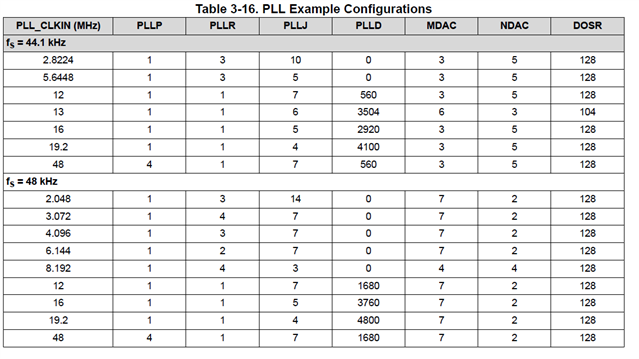

I'm not sure if the PLL is auto-detecting, the reference app-note provides some common configurations.

Could you provide the PLL settings (PLLP, PLLT, PLLJ, PLLD, MDAC, NDAC, DORS) for the case of 22.05KHz and 16-bit?

Thanks

Xiaoxiang

Hey Xiaoxiang,

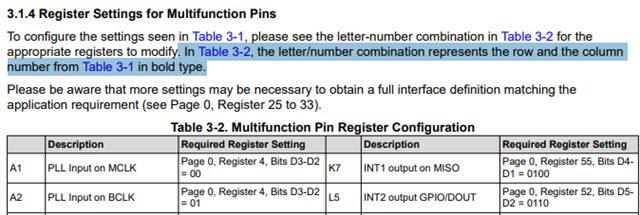

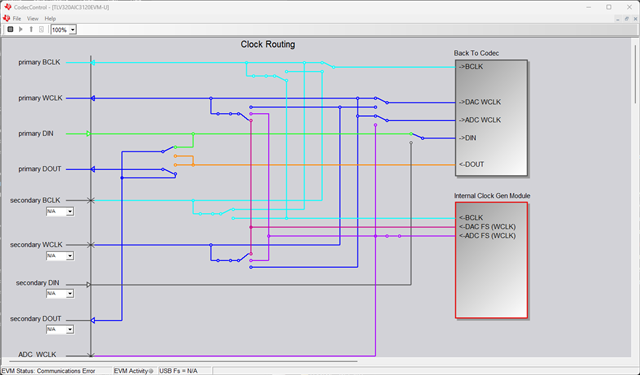

First use the A2 instructions to select BCLK as your input

Can you clarify in the thread how many channels you are using ? Also please clarify is the bit depth 16bit out of a wider word width ? for example 16 bit depth in 24 or 32 word width ? please clarify that as well.

Once done, I could guide you through a hack on how to select values in table 3-16 to get a working PLL tree.

If not response is given, I'll consider the thread closed.

Regards,

Ore.

Hi Ore,

Thanks for your support.

Our customer is attempting to configure. If there are any issues, I will consult you again.

Thanks

Xiaoxiang

Hi Ore,

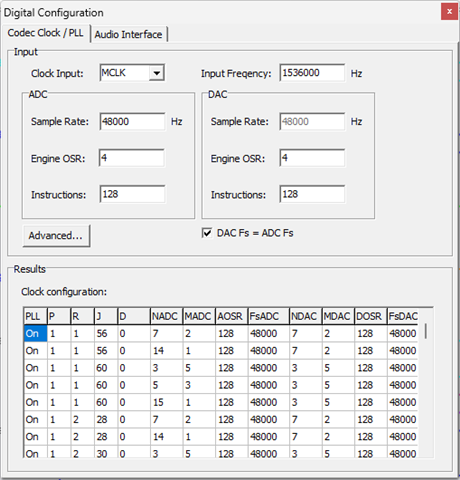

Our customer has made multiple attempts but still has some questions. Can you provide a case example? I have obtained some configurations: I2S , 16BIT depth, SAMPLE: 48KHZ, SCLK: 1.536MHZ. How should our TAS2505-Q1 be configured?

Thanks

Xiaoxiang

HI Xiaoxiang,

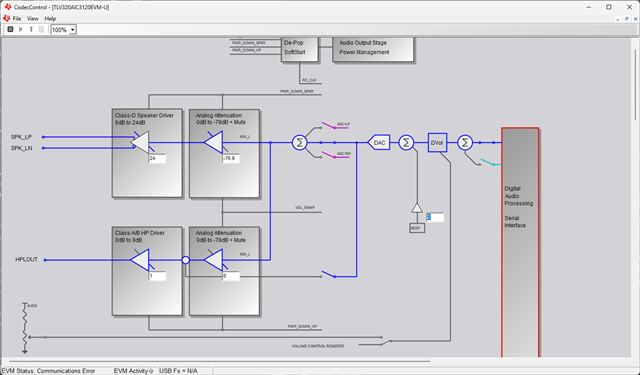

You may download AIC GUI from here: SLAC366 GUI for evaluation module (EVM) | TI.com

This can be used to calculate PLL settings.

Follow these instructions, for your specified example:

Let me konw if you have any questions.

Best regards,

-Ivan Salazar

Applications Engineer

Hi Ivan,

Thanks for your support.

Can we use only BCLK if MCLK is not available? I've noticed some audio playback anomalies with the customer, including sharp sounds, while some audio plays normally. I believe this is related to different sampling rates of the audio. The customer has some audio with a 48kHz sampling rate and some with an 18kHz sampling rate, but the customer reports that using the Aplay-Dplug parameters for playback will resample the audio.

Thanks

Xiaoxiang

HI Xiaoxiang,

Yes MCLK can be left floating and use BCLK as long as the BCLK frequency and Sample Rate requirements are compatible. BCLK frequency too low may not be usable.

You must verify that BCLK and WCLK signal frequencies are not changing for the different audio tracks. If these clocks change then a PLL settings would most likely have to change as well.

Best regards,

-Ivan Salazar

Applications Engineer

Hi Ivan,

This issue have been solved.

We update the PLL parameter, and we found their SOC-converted audio has distortion.

Thanks again.

Thanks

Xiaoxiang