Other Parts Discussed in Thread: OPA357

Tool/software:

Hello,

I am encountering an issue with my signal chain design and would appreciate some insights from TI engineers.

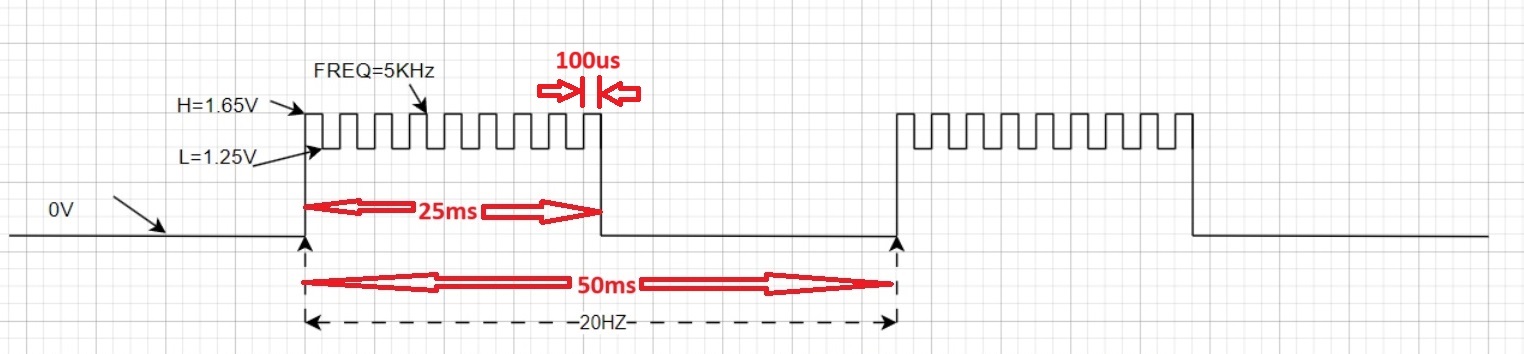

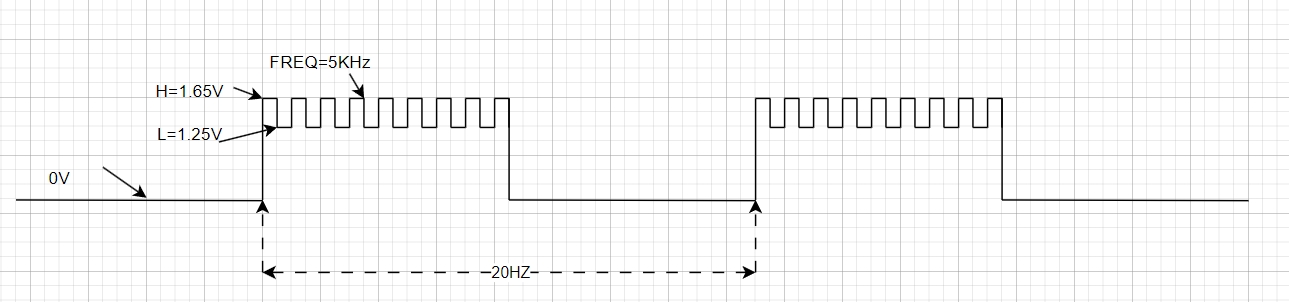

In my system, I am using an MCU with a DAC (STM32F072x8) that outputs a 20Hz square wave, ranging from 0V to 1.65V (i.e., 50ms high level and 50ms low level). On the high level of this square wave, I superimpose a 5kHz square wave with an amplitude range of 1.25V to 1.65V. There are 64 cycles of the 5kHz square wave during each high level.

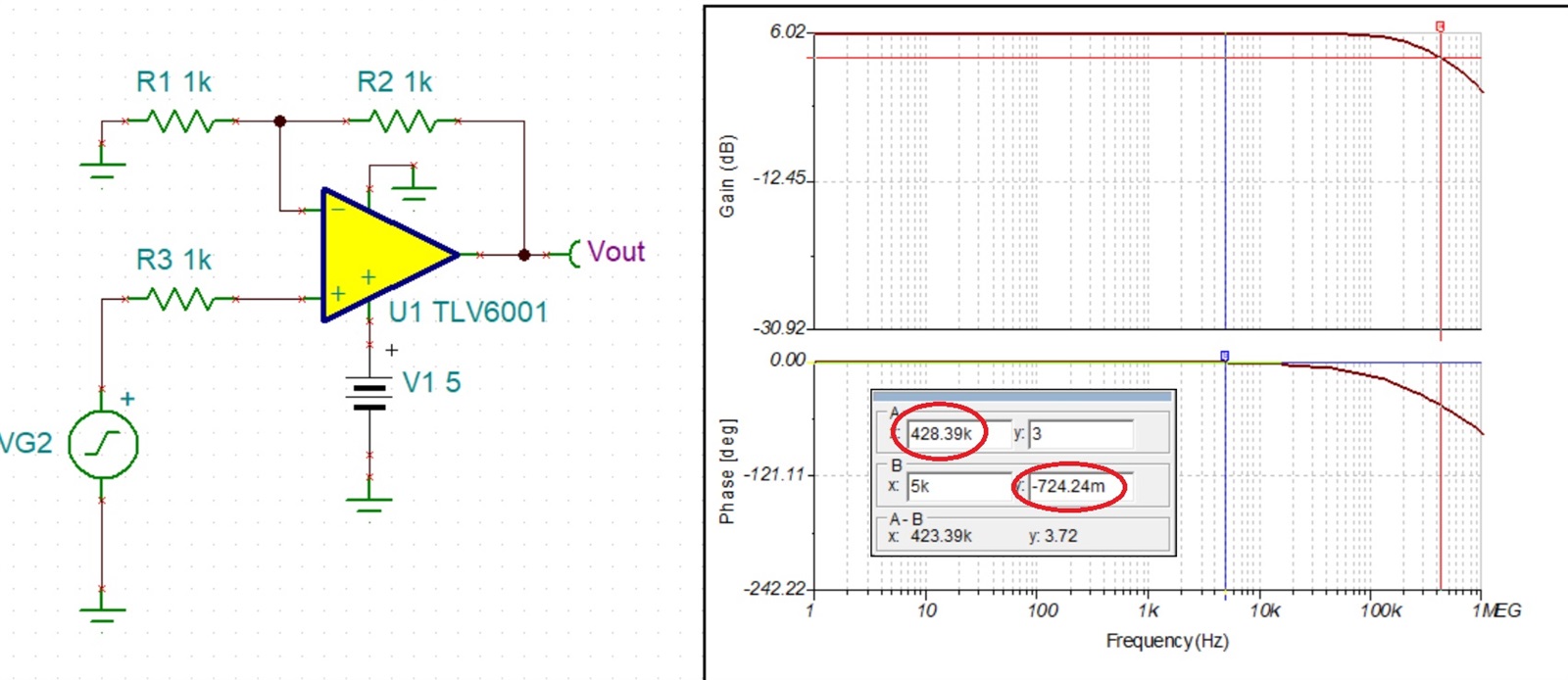

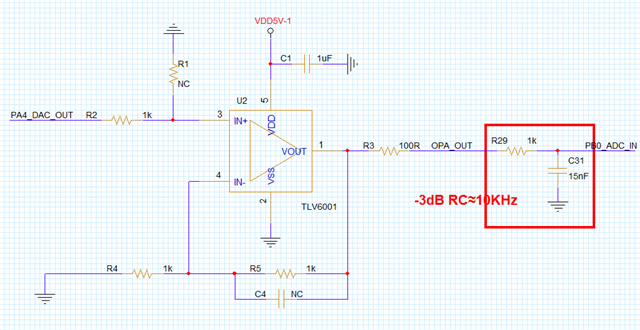

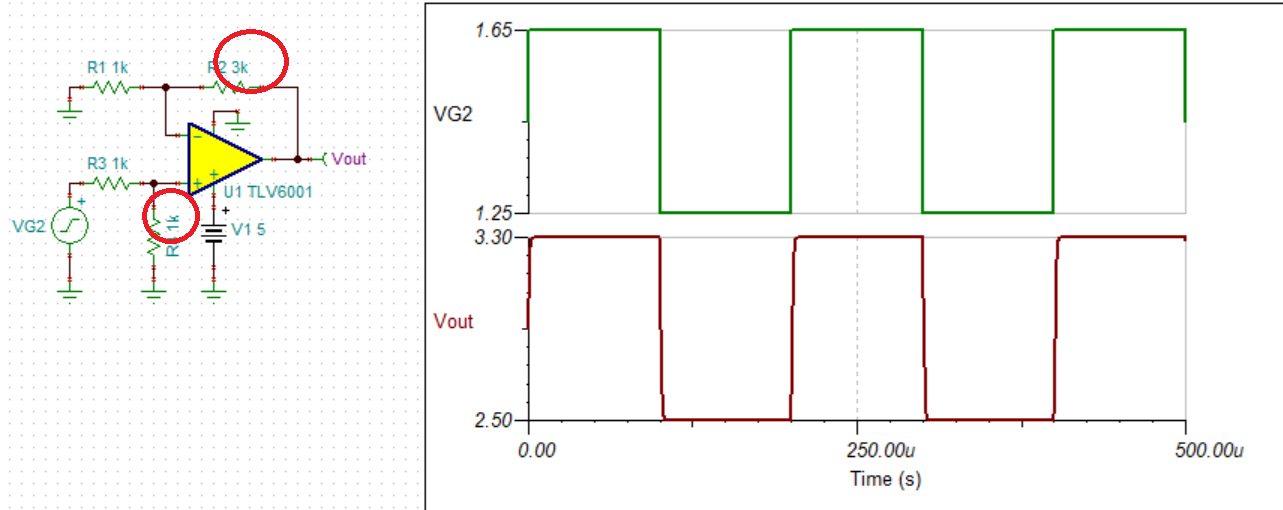

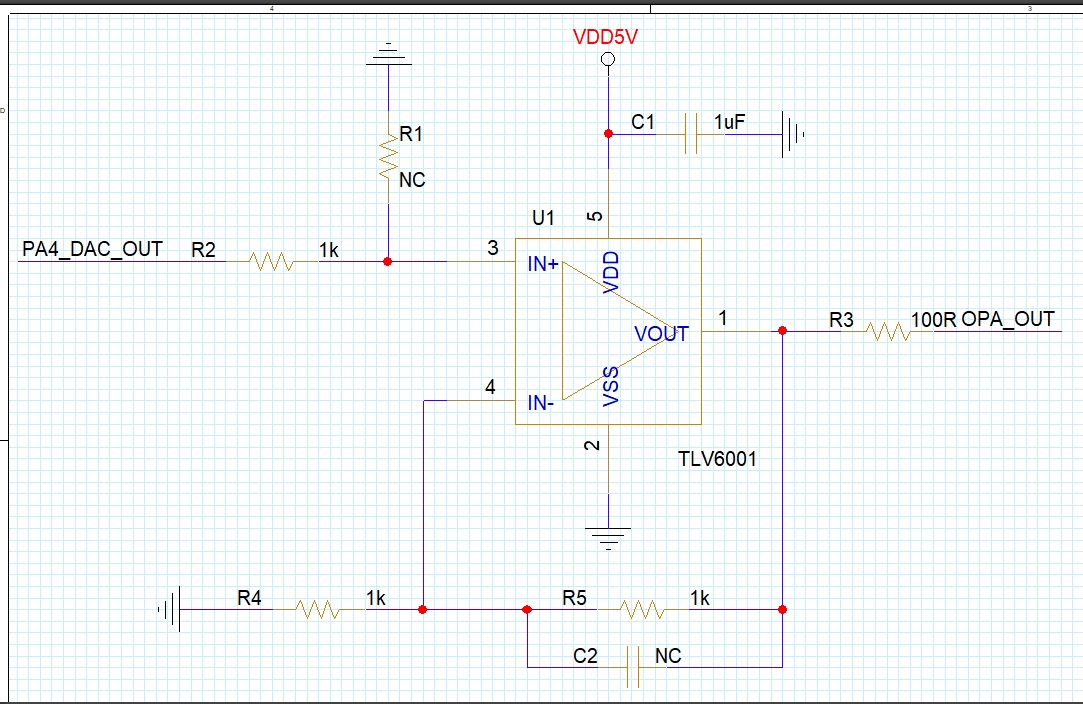

The signal passes through a closed-loop non-inverting amplifier with a gain of 2, using a TLV6001 op-amp (with a GBW of 1MHz). The amplified signal is then fed back into the MCU's ADC for phase measurement. The measurement takes place during the high level when the 5kHz square wave is present, and FFT is used to compute the phase.

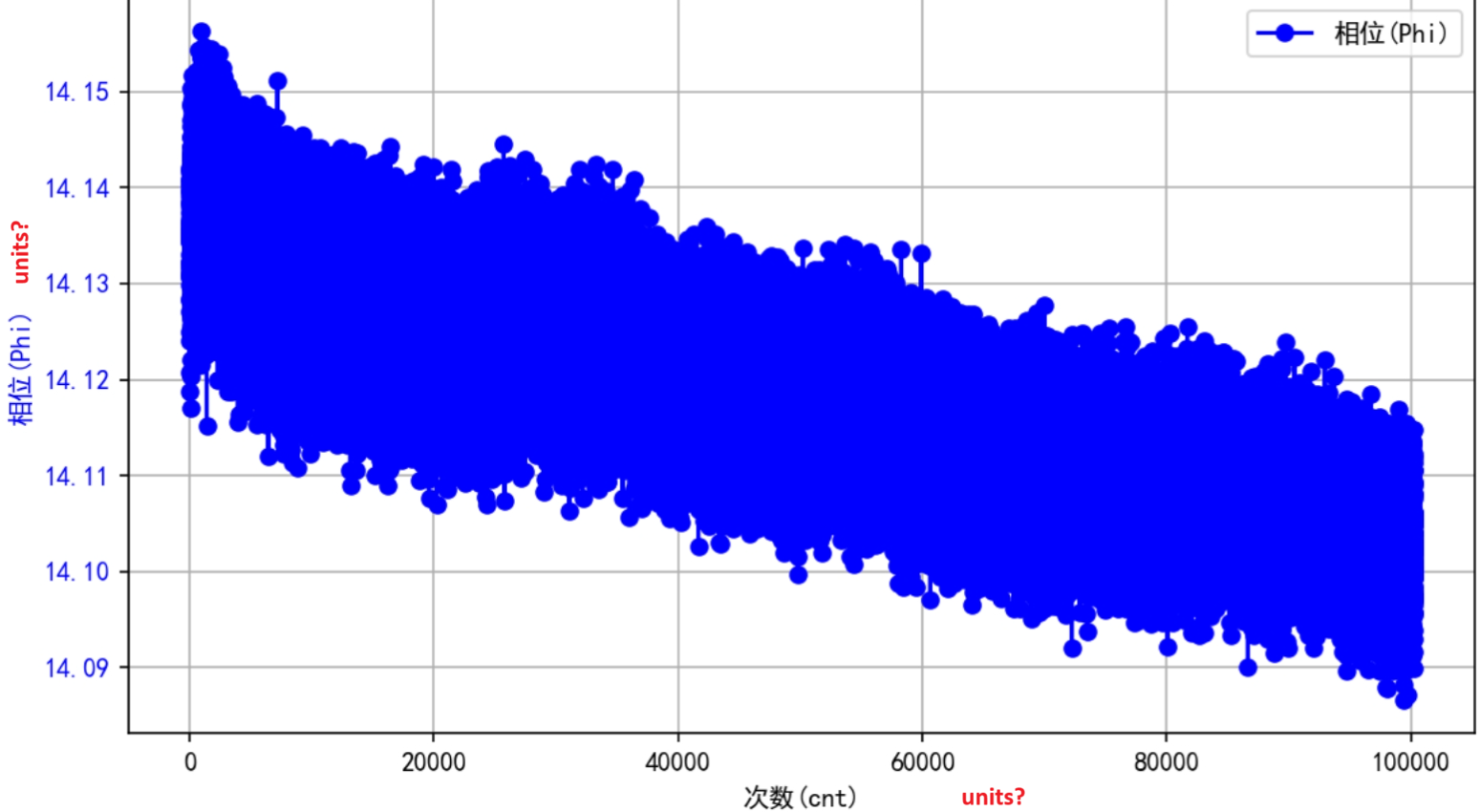

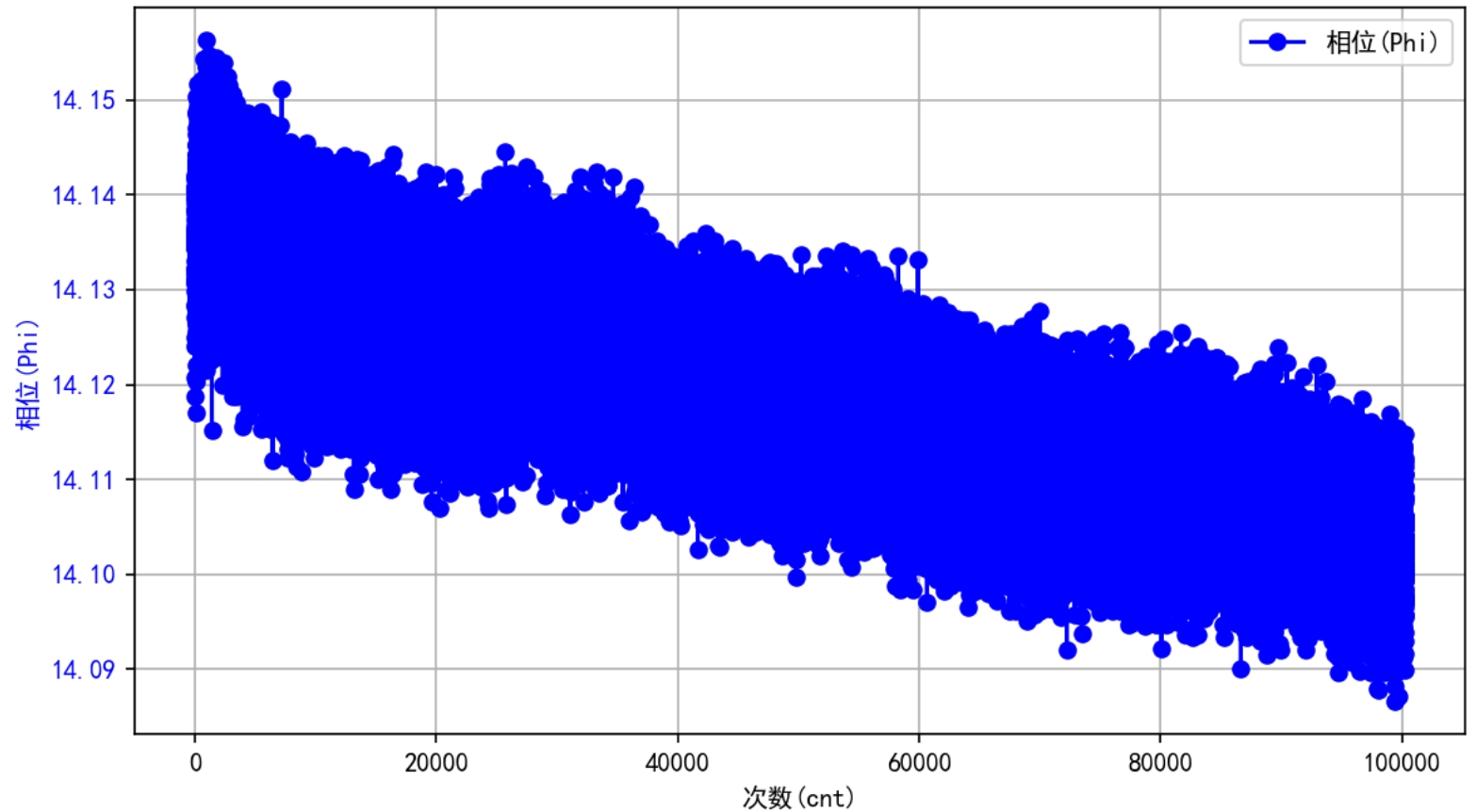

The issue I am facing is that as the number of measurements increases, I observe that the phase of the system gradually decreases—approximately 0.1° per 100W measurements. This is an unacceptable phenomenon in my current system.

To address this issue, I have tried the following approaches:

-

Replacing the TLV6001 op-amp with an OPA357 (250MHz) and enabling the EN pin.

-

Disabling the op-amp after each high-level measurement and re-enabling it before the next measurement.

-

I also tested the system by removing the op-amp and directly connecting the MCU DAC output to the ADC input. Under the same environmental conditions and measurement setup, the phase remained stable, with no decay after multiple measurements.

-

The entire test environment was kept at a constant room temperature, with no temperature fluctuations during the tests.

I would like to understand the root cause of the phase decay. What could be causing this issue, and how can I resolve it? Additionally, if I were to simulate this in TINA, how should I set up the simulation to accurately replicate this behavior?

I would greatly appreciate any guidance from TI engineers.

Thank you!