Tool/software:

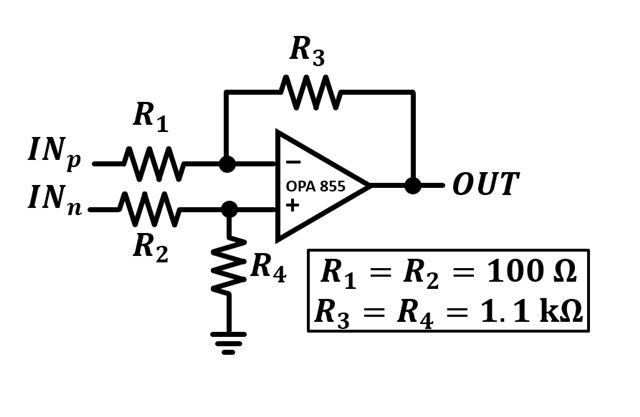

I wanted to use OPA855 to implement a wideband voltage subtractor from DC-100MHz. Here is the schematic that I use. The bias I use is VCC = 2.5V, VEE=-2.5V. I have added enough decoupling caps on VCC and VEE. When I powered it on, I saw that both INp and OUT have a DC value of -1.6V. INn has 0V DC. I plugged all INp, INn and OUT to the spectrum analyzer and did not see any tones (no oscillation). Could anyone help to debug the circuit?