Part Number: LMC6042

Tool/software:

Hello,

I have a buffer design that I sometimes see instability on. This is actually installed in a product which we have a significant samples size of. Early builds do not easily show the instability, but the latest builds are more likely to become unstable.

After simulating the circuit in spice, i've found that the design is on the edge of acceptable phase margin, my question is why would some samples be more stable than others. Is it process related?

Here's the circuit.

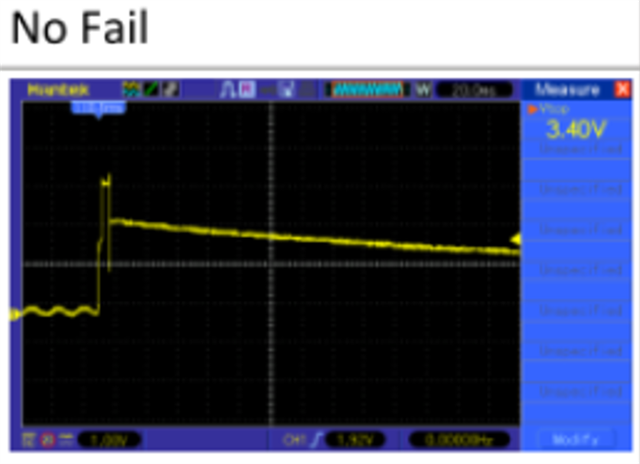

Here are actual in system results.