Tool/software:

Hi,

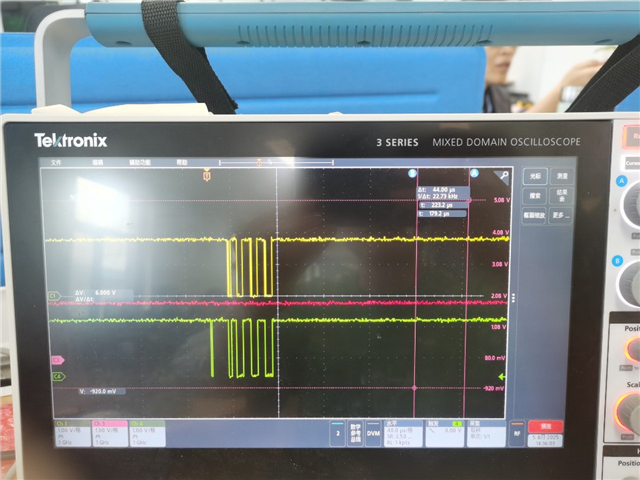

We have found that use CS0 (connected to 8-wire NAND flash) and CS1 (connected to 4-wire NOR flash) may result in chip selection conflicts, as shown in the waveforms of CS0 and CS1 in the following figures.

After replacing the TI EVM with CS0 (connected to 8-wire NAND flash) and CS3 (connected to 4-wire NOR flash), it works normally.

Why do CS0 and CS1 have conflicts.