Other Parts Discussed in Thread: STRIKE

Tool/software:

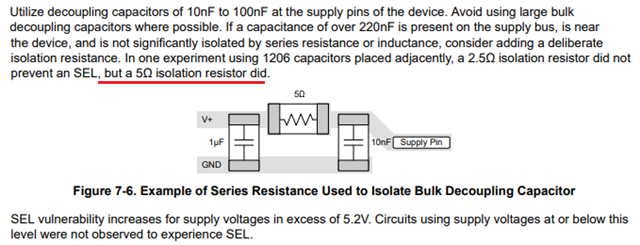

I'm seeking clarification on a statement within SNOAA62B LMP7704-SP SEE Report (Rev. B), where section 7.3 mentions "SEL vulnerability increases for supply voltages in excess of 5.2V. Circuits using supply voltages at or below this level were not observed to experience SEL."

To clarify: were the circuits tested below 5.2V supply using any of the SEL prevention techniques listed in 7.3? And does SEL vulnerability exist in applications where supply voltage is above 5.2V despite SEL prevention techniques being used?

Thank you,