Tool/software:

Hi Experts,

Can you help us fixed this issue of the model?

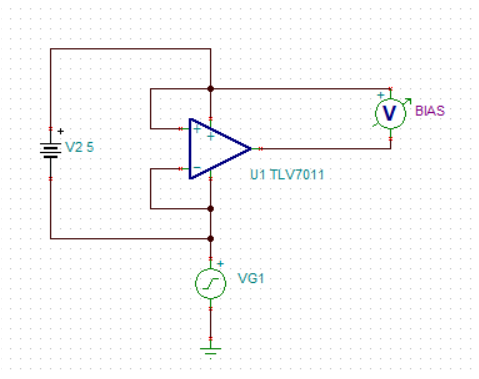

As you can see, the supply of TLV7011 is fixed to 5V, and by connecting the inputs IN+ and IN- to Vcc and Vee, respectively, will not violate the common-mode (though this is comparator, CM might not an issue).

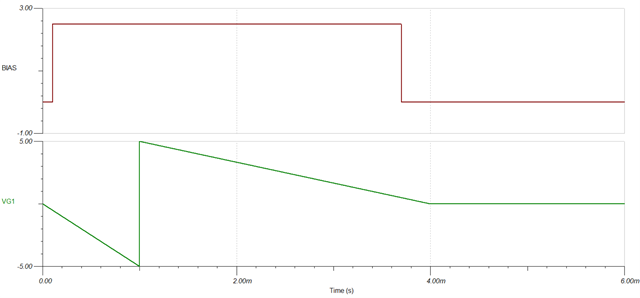

No matter how the VG1 supply is changing [(0 to -5V @ 1ms), then (-5V to 5V @1ms)...with the set-up above, the output should always equal to Vcc.

Thus, expecting for the voltmeter (BIAS) to be always equal to zero (since Vout should be equal Vcc).

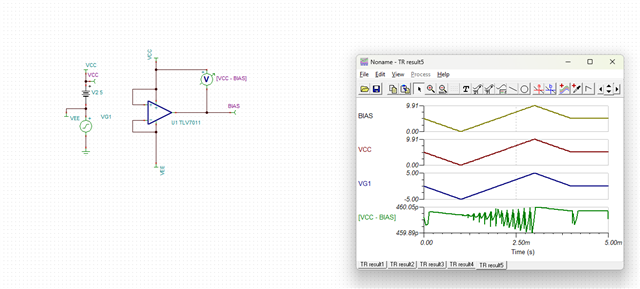

But the result is different:

Can you support this issue?

Regards,

Archie A.

PS: The application is as a gate driver for a PMOS 1.8V rail switch. The comparator's negative rail (V-) is driven by a charge pump inverter so as to supply sufficient gate drive to the MOSFET.