Part Number: OPA397

Other Parts Discussed in Thread: OPA328, ADS131A04, TINA-TI

This is a follow-up for my previous question here: ADS131A04: Using REFP on analog input pins for TIA design - Data converters forum - Data converters - TI E2E support forums

As suggested in the replies, I am looking to add a buffer to the REFP output of the ADS131A04 to ensure the current sourcing capabilities are sufficient. However, I am unsure how to choose the OpAmp exactly. Naively, I would expect e.g. the OPA397 to work, but it's unclear to me whether the bandwidth is sufficient to handle the rapid switching of the ADC sampling circuit? Would I need a faster OpAmp such as the OPA328, or something even faster?

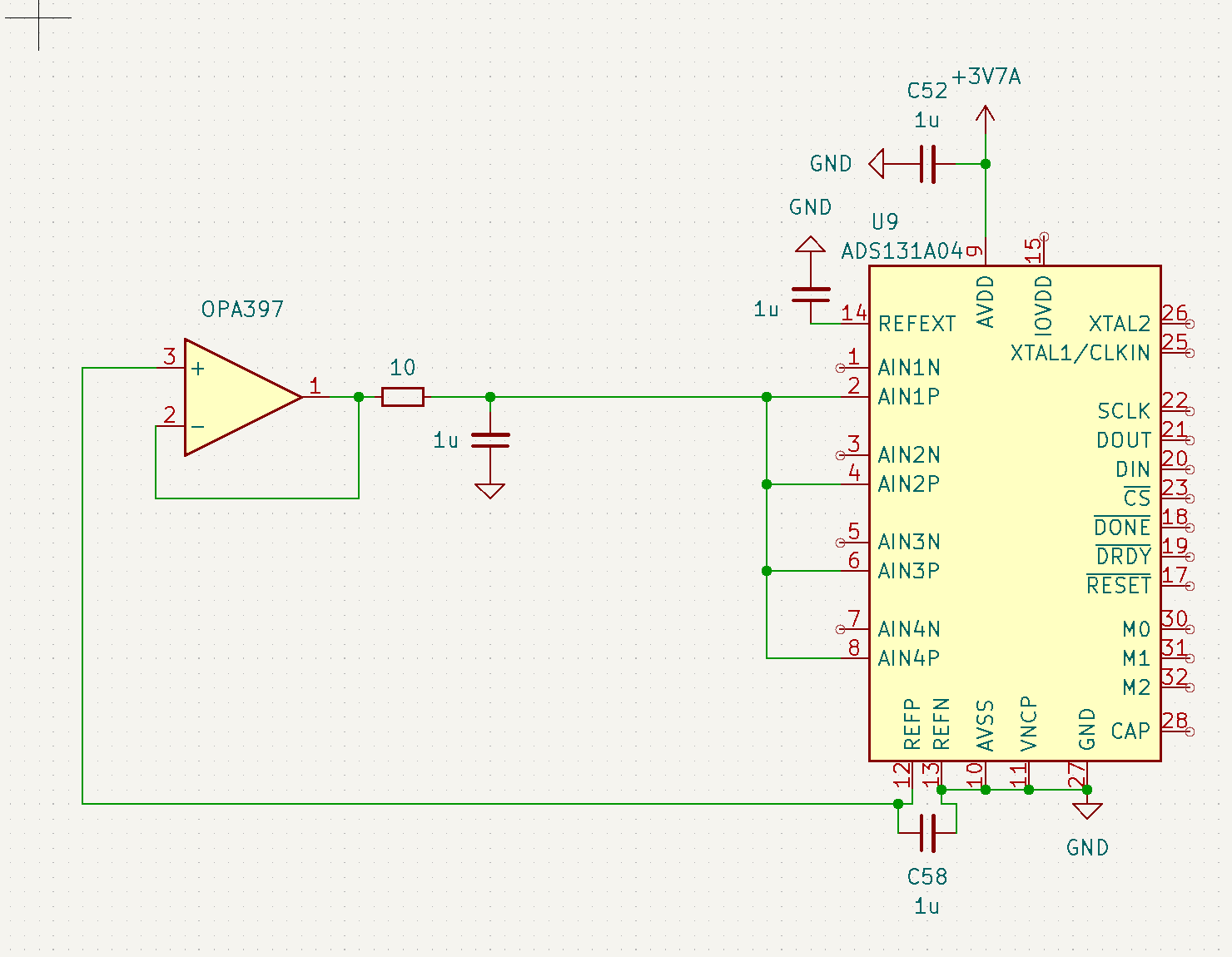

For clarity, this is the circuit I am envisioning (the negative ADC inputs would be wired to the actual signal):

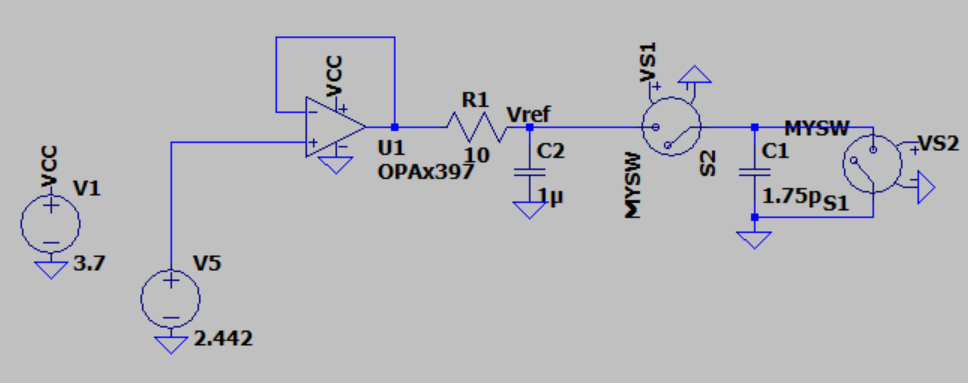

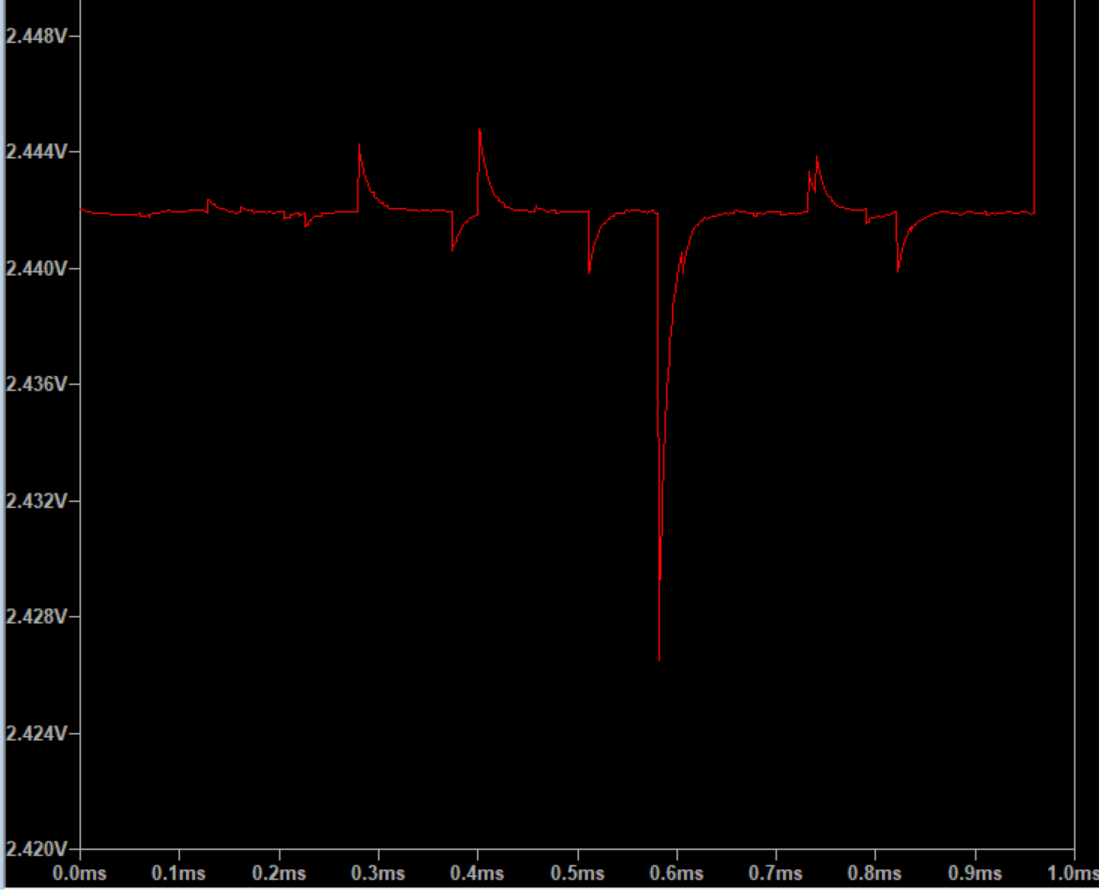

The lowpass after the buffer is there because I was worried about instabilities with the purely capacitive load from the ADC on the OpAmp (some rough LTSpice simulations seem to support this). I also tried to simulate the circuit to see whether the OpAmp is suitable, but I get some huge spikes from time to time, making me worried that something is wrong:

This is based on the circuit from Figure 38 from the ADS131A04 datasheet. The switches are set to 4MHz with an on-time of 0.12us, 180° out of phase.

What concerns me is that there are these random jumps away from the steady state (this is measuring the voltage at Vref, i.e. the input of the ADC):

So, in summary:

- Is the OPA397 suited to buffer the ADCs REFP output for the ADC inputs? If not, what would be a better choice?

- Do I need the lowpass filter after the buffer? Are the values reasonable?

- In general, how can I verify that a given ADC is suitable, i.e. how do I model the ADC circuitry, and what do I need to look for?