Hello,

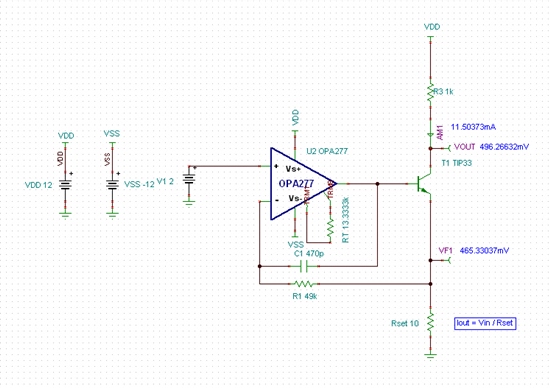

We are using OPA 2277 to drive a N-channel MOS transistor in linear mode. It is configured with negative feedback to stablize the transistor current. We provide the op-amp with dual power supplies (+12/-12). The purpose of this circuit is to generate a stable current with the step voltage to the op-amp input. How does the output common voltage affect the driving capability? Are there any limitations? The transistor threshold voltage is 2.0-4.5V. The transistor can handle up to 90A at ambient temperature.

Thank you

Johnny