Other Parts Discussed in Thread: XTR111

I am working on a new product design using the XTR111 to implement a 4-20 mA current loop output.

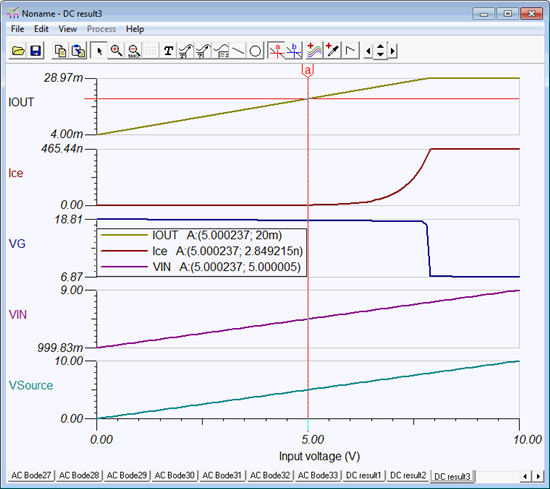

The data sheet recommends two different external current limit circuits - Figures 37a and 37b. The simpler circuit of 37a uses one extra PNP transistor (Q2), but has a potential downside of leakage current through Q2 causing an error in the desired output current value. It appears that a high current will start to turn on Q2, which will decrease the gate/source voltage to Q1 and limit the current using Q1.

Question 1: Is there an easy way to quantize the leakage current to determine the magnitude (percentage) of the error? Is there an alternate but similar circuit that would have nearly zero leakage current until "tripped" by a high current?

The series circuit of 37b may be attractive because it eliminates the potential leakage current error. However, now Q3 is in the direct current path with the MOSFET and provides the current limiting, which raises a concern about power dissipation. My circuit design uses a heat sink on the MOSFET (Q1) to handle the steady-state loop power dissipation, which could approach 1 watt under worst case conditions (max loop current and high loop driving voltage). When the loop current is low, Q2 should be OFF, and therefore Q3 should be saturated and have little voltage drop/power dissipation. If, however, the MOSFET were forced into a fully saturated (low impedance) state for some reason, then it appears that the current limit circuit would kick in, and Q3 would have to dissipate all of the power. I would like to use a SOT-23 packaged MMBT2907A for Q2 and Q3, as I don't have room for another large transistor with heat sink.

Question 2: Is the current limit circuit only to protect against a short-duration turn-on transient, and therefore Q3 will have low average power dissipation, or should Q3 be sized for high current and require a heat sink as well?